## **CHARACTERIZATION OF SERVER THERMAL MASS**

Electronics

DECEMBER 2013 electronics-cooling.com

o ten ce la adult fr i data all'argenda di Tata dista all'argenda di Tata dista tet dopologi FEATURES COOLING THE CLOUD:

ENERGY-EFFICIENT WARM-WATER COOLING OF SERVERS

THERMAL MANAGEMENT OF MANY-CORE PROCESSORS USING POWER MULTIPLEXING

**9th Replacement**

**3rd Replacement**

**5th Replacement**

**12th Replacement**

# It's Lights Out Again. Do You Really Want To Take Your Brand Integrity **Down This Road?**

#### Bergquist Thermal Clad<sup>®</sup> keeps your LEDs intense, bright and reliable wherever they go.

#### Built for long-term reliability.

Choosing the right IMS (insulated metal substrate) can make the difference of a successful product or not. Knowing the long term performance and reliability of the materials in your design, will give your customers

a quality product and protect your reputation. This includes:

- Thermal impedance, not just thermal conductivity

- Long-term dielectric strength, not just breakdown strength

- U.L. Listed

- Long-term temperature testing

#### A balance of innovative thinking and expertise.

Not all substrate materials have the Bergquist company's 25+ years of testing and proven field performance. Our testing is geared to the application, not just numbers, which give a true performance picture you can count on in your design.

#### Bergquist delivers cooler performance for Power LEDs.

Dielectrics: Bergquist offers a wide selection of dielectric and thickness choices to meet the demanding specs of high performance applications (Bergquist HPL and HT versions), as well as, lower performance requirements (Bergquist MP, HR T30.20 versions).

Base Plates: Bergquist offers a wide range of thicknesses, aluminum for packaged components and copper base for high power density and COB applications.

**Circuit Copper:** From 35µm to 350µm (1/2 oz. to 10 oz.)

Call or visit us to qualify for a FREE T-Clad Samples Kit: www.bergquistcompany.com/coolkit

#### 1.800.347.4572 www.bergquistcompany.com

952.835.2322 fax 952.835.0430 18930 West 78th Street • Chanhassen, Minnesota 55317

Thermal Materials • Thermal Substrates • Fans and Blowers

## **CONTENTS**

#### 2 Editorial

Madhusudan Iyengar, Editor-in-Chief, December 2013

#### 4 COOLING MATTERS

Clay in Supercapacitors; New Heat Exchanger for Better Liquid Cooling; New Helium Cooling Technology; and more

#### 6 THERMAL FACTS & FAIRY TALES

#### Evolving the Role of the Thermal Engineer from Analyst to Architect

Scott Johnson, Raytheon Space and Airborne Systems Brendon Holt, Raytheon Missile Systems

#### 8

#### **TECHNICAL BRIEF**

Thermal Packaging From Problem Solver to Performance Multiplier *Avram Bar-Cohena*, Microsystems Technology Office Defense Advanced Research Projects Agency (DARPA)

#### 12 CALCULATION CORNER

Use of JEDEC Thermal Metrics in Calculating Chip Temperatures (without Attached Heat Sinks) *Bruce Guenin,* Assoc. Technical Editor

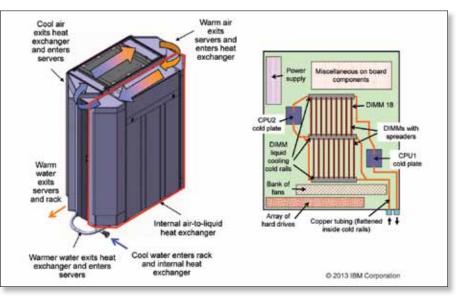

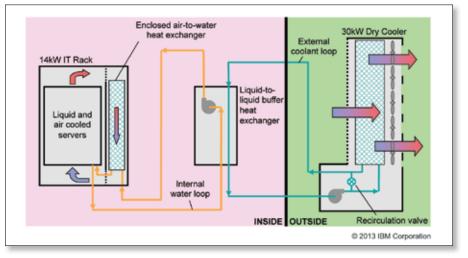

#### Milnes P. David, Robert Simons, David Graybill, Vinod Kamath, Bejoy Kochuparambil, Robert Rainey, Roger Schmidt, IBM Systems & Technology Group, Poughkeepsie NY and Raleigh NC Pritish Parida, Mark Schultz, Michael Gaynes, Timothy Chainer, IBM T. J. Watson Research Center, Yorktown Heights NY

#### FEATURED ARTICLE

#### 18 THERMAL MANAGEMENT OF MANY-CORE PROCESSORS USING POWER MULTIPLEXING

*Man Prakash Gupta, Satish Kumar G. W. Woodruff School of Mechanical Engineering Georgia Institute of Technology*

#### 24 CHARACTERIZATION OF SERVER THERMAL MASS Mahmoud Ibrahim, Panduit

30 SEMI-THERM 30 ADVANCE PROGRAM

40 INDEX OF ADVERTISERS

**DECEMBER 2013**

# Editorial

Madhusudan lyengar, Editor-in-Chief, December 2013

Research & I agement over th microprocessor

**ECENTLY I READ AN ARTICLE** on cutting-edge research demonstrating the feasibility of data storage on media for a million years! A few years ago this might not have resonated with me as a thermal engineer working to cool electronics, but now it does. Let me explain why.

Research & Development on IT equipment thermal management over the past few decades has justifiably focused on microprocessor (CPU) based systems. This may be explained by increased CPU transistor density, as per Moore's law, hence rising heat fluxes. However, in parallel, the growth rate of stor-

age hardware that complements the compute engine (i.e., microprocessors) has been dramatic in recent years, not only in data centers that support internet based products and services (e.g. social media, photo/video hosting, utility/cloud computing, e-commerce), but also in the governmental, medical, and industrial sectors. While microprocessors come and go with new electronics hardware, the expectation for how long the data need to be stored for can easily range from decades to a lifetime to potentially centuries (e.g., in the case of historic and scientific data). As humans with intricately embedded electronics, we generate and use data at an ever increasing rate. This should not come as a surprise to any of us, engineers or otherwise, based on our own data storage needs at work or at home. On a personal note, I own several storage devices ranging from CDs and consumer disk drive devices to DVDs. The number of storage devices has continuously grown rapidly over the last few years, especially with the addition of so many photographs of my daughter since her birth.

So, why should this matter for a thermal engineer in the electronics cooling field? In addition to cooling traditional electronic devices and systems, some of us are responsible for reliably cooling storage devices and systems (and data centers). Storage devices could be made of magnetic media (tapes or rotationally spinning disk drives) or silicon (flash) or something else. As an example, a common form factor for hard disk drive with spinning magnetic media is 4" by 6" by 1", with a power in the range of 10 W and maximum case temperature of approximately 60°C. By itself, this thermal management problem is a piece of cake for a thermal engineer, but consider hundreds or thousands or millions of such drives closely packed with each other, with fan-based air cooling doing the job. Now consider that some of the devices store "hot" or active data, and others store "cold" or inactive data. Each of these storage tiers have different cooling needs over their lifetime. I anticipate that this area of thermal engineering will increase in importance in the coming years, and I thus wanted to use my editorial capital for this issue to discuss this topic with the ElectronicsCooling audience.

For this edition of the magazine, I am excited to offer the readers several interesting topics such as justification for embedded liquid cooling for very high performance microprocessors, numerical analyses to investigate the concept of intentional transient power manipulations in microprocessor cores, transient thermal characterization of servers, and highly energy-efficient liquid cooling systems for data center facilities. In addition, we have our traditional favorites, which are the calculation corner and the thermal facts and fairy tales sections. I hope that you enjoy this stimulating issue of *Electronics Cooling* and would like to offer you all my warmest wishes for a great holiday season. Stay warm or cool based on your preference, but I hope it is thermally energy efficient!

www.electronics-cooling.com

#### **ASSOCIATE TECHNICAL EDITORS**

Bruce Guenin, Ph.D. Principal Hardware Engineer, Oracle bruce.guenin@oracle.com

Madhusudan Iyengar, Ph.D. Thermal Engineer, Facebook grashof@yahoo.com

Peter Rodgers, Ph.D. Professor, The Petroleum Institute prodgers@pi.ac.ae

Jim Wilson, Ph.D., P.E. Engineering Fellow, Raytheon Company jsw@raytheon.com

#### PUBLISHED BY

ITEM Media 1000 Germantown Pike, F-2 Plymouth Meeting, PA 19462 USA Phone: +1 484-688-0300; Fax:+1 484-688-0303 info@electronics-cooling.com; electronics-cooling.com

#### **CONTENT MANAGER**

Belinda Stasiukiewicz bstas@item-media.net

#### **BUSINESS DEVELOPMENT MANAGER**

Casey Goodwin cgoodwin@item-media.net

#### **GRAPHIC DESIGNER**

Evan Schmidt eschmidt@item-media.net

#### **EDITORIAL ASSISTANT**

Aliza Becker abecker@item-media.net

#### PRESIDENT

Graham Kilshaw gkilshaw@item-media.net

#### REPRINTS

Reprints are available on a custom basis at reasonable prices in quantities of 500 or more. Please call +1 484-688-0300.

#### SUBSCRIPTIONS

Subscriptions are free. Subscribe online at www.electronics-cooling.com. For subscription changes email info@electronics-cooling.com.

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, or stored in a retrieval system of any nature, without the prior written permission of the publishers (except in accordance with the Copyright Designs and Patents Act 1988).

The opinions expressed in the articles, letters and other contributions included in this publication are those of the authors and the publication of such articles, letters or other contributions does not necessarily imply that such opinions are those of the publisher. In addition, the publishers cannot accept any responsibility for any legal or other consequences which may arise directly or indirectly as a result of the use or adaptation of any of the material or information in this publication.

Electronics Cooling is a trademark of Mentor Graphics Corporation and its use is licensed to ITEM. ITEM is solely responsible for all content published, linked to, or otherwise presented in conjunction with the Electronics Cooling trademark.

## MALICO Special line attachment maker

Malico is not an ordinary company, It's unique and extra ordinary product driven not profit driven. Our products are so carefully made and almost zero defect. We take extreme care of every part in our products. So, Our products are so reliable and fool prove. You can rely on us 100% for using our products and care free. Let's grow together in the industry and be prosperous.

Contact offices:

Boston , MA Tel: 978-771-9285 Chino CA Tel: 909-598-3738 Dallas , TX Tel: 214-514-9836 14776 Yorba Ct. , Chino , CA 91710

#### www.malico.com

# **Cooling Matters**

Applications of thermal management technologies

#### **RESEARCHERS: CLAY IS KEY INGREDIENT IN HIGH-TEMP. SUPERCAPACITORS**

Clay, an abundant natural material, may hold the answer to developing super hightemperature supercapacitors for powering devices in extreme environments, says new research from Rice University.

According to a report, the supercapacitor created by researchers at Rice University using naturally-occurring clay and room temperature ionic liquids (RTIL) is reliable at temperatures of up to 200°C (392°F), and possibly higher. With such a tolerance, the new supercapacitor design could help raise temperature restrictions on devices used in oil drilling, military and space applications.

The Rice University team created a paste comprised of a room-temperature ionic liquid (RTIL) first developed in 2009 with natural Bentonite clay. The paste was then sandwiched between layers of reduced graphene oxide and two current collectors to form the supercapacitor. Tests and subsequent electron microscope images showed very little change in the paste material after it was heated up to 300°C. Researchers also observed that despite a slight drop in capacity observed in the initial charge/discharge cycles, the supercapacitor remained stable through 10,000 test cycles.

**Source: Scientific Reports**

## Datebook.

#### **Electronics Packaging Technology Conference SINGAPORE, TAIWAN**

www.clocate.com/ conference/15th-Electronics-Packaging-Technology-Conference-EPTC-2013/28329/

#### 'ELECTRONIC BLOOD' POWERS AND COOLS BRAIN-INSPIRED COMPUTER

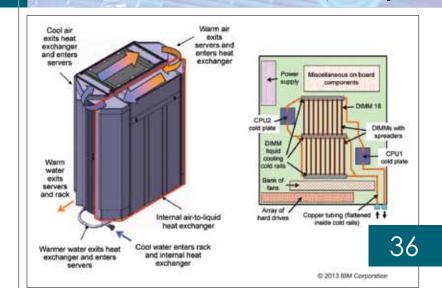

IBM has unveiled a prototype of a new brain-inspired computer powered and cooled by what the company is calling "electronic blood." The company says it is learning from nature in an effort to develop small, highly efficient computing system.

"We want to fit a supercomputer inside a sugar cube," IBM researcher Bruno Michel, Ph.D., told the BBC. "To do that, we need a paradigm shift in electronics— we need to be motivated by our brain."

According to Michel, the human brain is able to consume energy at a low rate "because it uses only one—extremely efficient—network of capillaries and blood vessels to transport heat and energy—all at the same time." The new IBM prototype computer emulates this concept using "redox flow" system, which pumps an electrolyte "blood" through the computer. The liquid is charged via electrodes and pushed into the computer, where it discharges energy to the processor chips and then carries heat away.

Ultimately, IBM hopes to shrink a one petaflop computer-which would fill half a football field today-down to the size of a standard desktop computer by 2060, and one day use its "electronic blood" concept to achieve zettascale computing.

MIT RESEARCH DISCOVERS **NEW SURFACES EASE THE DISSIPATION OF EXTREME HEAT**

A new method of cooling extremely hot surfaces more effectively from researchers at MIT could benefit industrial equipment and electronic devices.

Liquid cooling is commonly used in a number of applications. MIT researchers developed a way to keep the water droplets from bouncing as part of a method to cool hot surfaces more effectively.

The method involves adding tiny microscale silicon posts to a smooth silicon surface to create a textured surface.

Source: MIT

A micrograph showing water droplets landing on specially designed silicon surfaces at different temperatures. At higher temperatures, the droplets begin to exhibit a new behavior: instead of boiling, they bounce on a layer of vapor, never really wetting the surface

Source: BBC

#### **DECEMBER 11-13**

#### **Consumer Electronics** Show 2014 LAS VEGAS, NEV., US

www.cesweb.org

**JANUARY 7-10**

#### **FEBRUARY 5-6**

9th European Advanced **Technology Workshop** on Micropackaging & **Thermal Management** LA ROCHELLE. FRANCE www.france.imapseurope.org

#### **MARCH 9-13**

SEMI-THERM SAN JOSE, CALIF., USA www.semi-therm.org

#### NEW HEAT EXCHANGER RESEARCH COULD LEAD TO BETTER LIQUID COOLING

A New Mexico State University assistant professor is investigating methods of increasing heat exchanger efficiency that could enable space missions to remain in orbit for longer periods of time and lead to better automotive, defense, data center and power generation thermal management systems.

Currently, the length of space missions is severely limited because of the gradual loss of cryogenic propellants due to boil-off caused by solar heating. Thus far, the team has found that under certain operating conditions, cryogenic heat exchangers could be reduced to at least one-third the size of current models, with more than 10-15 percent improvement in thermal performance. In cooperation with Brian Motil, chief of the Fluid Physics and Transport Branch of NASA GRC, they are working to integrate their findings into cryocooler systems.

Source: The El Paso Times

#### HIGH TEMPERATURE CAPACITORS REMOVE NEED FOR EV COOLING SYSTEMS

A new lead-free, high temperature ceramic capacitor developed by scientists at the National Physical Laboratory UK could improve the efficiency and reliability of electric and hybrid vehicles by enabling the removal of heavy complex cooling systems.

NPL researchers claim their new material, called HITECA can hold more energy and function at much higher temperatures—over 200°C—than conventional capacitors. HITECA is made from a ceramic paste with a granular stucture comprising a bismuth ferrite (BiFeO3) compound doped with strontium-titanate (SrTiO3). The NPL research team is now looking to test the capacitor technology in an electric vehicle power electronics system.

Source: The Engineer

#### SONY RELEASES SOURCE CODE FOR THERMAL MANAGEMENT SOLUTION

Sony has released the source code for Thermanager, a thermal management solution developed for and used in the company's Android Open Source Project (AOSP) for Xperia projects. The source code is available through the Sony channel on GitHub.

"Thermal management for these projects has been handled by binaries released through Developer World. While this solves the immediate problem of devices overheating, it does not provide developers a way to customize, improve or analyze the behavior of this important part of the system," the company said in a recent statement.

#### NEW COOLING TECHNOLOGY FOR MRI MACHINES OFFERS HELIUM ALTERNATIVE

A new way to cool magnets to the extremely low temperatures needed for MRI machines may hold the answer to overcoming the effects of the increasing global helium shortage. Well-known for its use in party balloons, helium is also used in the cooling of superconducting magnets, with the main commercial application being in MRI scanners and particle accelerators. Now, a company called Cryogenic has developed a technique to cool magnets that requires only a small fixed amount of helium—approximately half a liquid liter—and mechanical coolers which run using electrical power and cooling water.

Source: Wired

#### **APRIL 7-9**

IEEE Euro-SimE GHENT, BELGIUM http://www.eurosime.org

#### APRIL 27-MAY 1

International Thermal Conductivity Conf. and International Thermal Expansion Symposium WEST LAFAYETTE, IND., US www.thermalconductivity.org

#### MAY 7-9

Source: SONY

Smart Lighting 2014 BARCELONA, SPAIN www.smartlighting.org

#### **JUNE 2-5**

#### Thermal Imaging Conference 2014

LAS VEGAS, NEV., US www.thermalimaging conference.com

## **Evolving the Role of the Thermal Engineer from Analyst to Architect**

Scott Johnson, Raytheon Space and Airborne Systems Brendon Holt, Raytheon Missile Systems

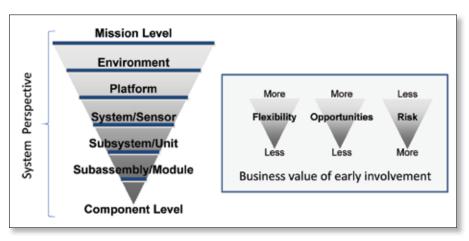

**VOLVING TRENDS** within the aerospace industry are creating a new set of challenges that directly influence thermal management choices and planning that should be addressed in the early phases of the product development process. Within the functional side of the aerospace industry, the term "system architect" has been created to describe individuals with expertise in subsystem design, acquisition and integration. Hence, it is the position of the authors that the role of the thermal engineer must also evolve to have a similar systems perspective.

Based on past and recent experiences of the authors, there are four levels of interaction between thermal engineers and the product development process. These levels of thermal interaction fall into four categories:

- 1. *Thermal Analysis.* Interaction at this level is common to almost all product development efforts. The thermal engineer performs equation based and/or detailed thermal analysis using computational techniques and reports requirements compliance at the component level.

- 2. *Thermal Design*. This level of interaction is also common to most product development efforts. The thermal engineer works in parallel with product design team to provide balanced design solutions that enable compliance with thermal design requirements.

- 3. Thermal Systems Engineering. Interaction at this level is less common. The thermal engineer creates system level thermal performance models, uses these to derive and document thermal design requirements and then manages

**Scott T. Johnson** is an engineering fellow with more than 30 years of experience at Raytheon Space and Airborne Systems in El Segundo Calif., where he is part of the Mechanical and Optical Engineering Center (MOEC). Johnson specializes in system level thermal and thermodynamics management for military airborne and ground based sensors. Scott also specializes in the development of advanced thermal technologies for very high heat flux component design and holds multiple patents in this area. Johnson received his BSME degree from the University of Florida in 1981.

**Brendon R. Holt**, Ph.D. is currently a senior principle engineer at Raytheon Missile System in Tucson Az where where he is a thermal section head. He leads a group that is responsible for providing thermal engineering analysis, design and testing support for military land, sea, air and space systems. He has been at Raytheon and legacy Texas Instruments Defence Segment since 1995. He received his Ph.D. from the University of Texas at Arlington (1995) in Fluid Dynamics and Heat transfer with phase change.

execution by product design teams across all program phases (design, build, qualification, production).

4. Thermal Architect. Interaction between a thermal engineer and a product development activity at the architect level is desirable but infrequent. The thermal engineer engages during the pursuit and competition/capture phases of the program to determine the best over all thermal systems approach that satisfies program objectives. The au thors refer to this as Mission Level Engagement. Ideally, the thermal systems engineer and the thermal architect are the same individual.

The impact of where these roles are applied in the product development process is illustrated in the left side of Figure 1. The highest perspective is the mission level and the lowest the component level. Ideally, the thermal architect would be engaged at the mission level (or as close as possible) early in the program pursuit and capture phases. The thermal architect would then transition to the role of thermal systems engineer, deriving and documenting thermal requirements at the system level and then managing thermal design and analysis activities at the subsystem, subassembly and component level. In general, thermal management and design decisions made at higher levels afford the benefits of more flexibility, more opportunities for design optimization and synergy, and less risk. These benefits are illustrated by the

FIGURE 1: Levels of Thermal Management Interaction with Product Development.

smaller inverted pyramids on the right side of the figure.

At present, mission level engagement of the thermal architect is something of an idealization. Many product development activities simply are not structured to benefit from the engagement of a thermal engineer at the mission level. Also, mission level engagement of the thermal engineer would require something of a culture change within the industry and these are slow to occur. So in order to precipitate change in the culture the thermal engineer's skill and tool set will have to evolve beyond the traditional thermal analysis and thermal design roles into the role of the thermal systems engineer and thermal architect. When it comes to modeling, the attributes most critical to the thermal architect and systems engineer's effectiveness are speed and scalability. This means modeling only what is necessary and doing it quickly and with the needed accuracy and flexibility. This also means not being seduced by the siren's call of the "rainbow plots" created using modern computational fluid dynamics (CFD) and simulation codes too early in the program. The level of detail required for these object based models is typically not available during the early phases of the program when thermal management decisions have the most impact.

In 2011, one of the author's participated in a technology study derived from the Air Force Research Laboratories (AFRL) INVENT (Integrated Vehicle Energy Technology) initiative [1]. As part of the effort, a complete equation based transient model was created for a critical pod mounted sensor and integrated to run in MATLAB Simulink. This was combined with a platform (aircraft) level environmental cooling system (ECS) Simulink model and used to fly virtual missions. One of the objectives of the INVENT initiative was to extend this approach to integrate all of the platform critical energy subsystems. These would include energy "demand" functions like critical sensors and energy "supply" functions such as the engine, fuel delivery and electrical power generation subsystems. The benefit of this approach is true concurrent design at the mission level. The model evolves with the program and is used to actively manage the product development process. This is a real example of how a thermal engineer would function as a thermal architect engaging near the top of the System Perspective illustrated in Figure 1.

So what is the moral of this "facts and fairy tales" story. The fairy tale is that the role of the thermal engineer is defined entirely by thermal analysis. The fact is that acting as thermal architects, we have the opportunity to influence design choices at the earliest program phases in a way that maximizes product performance while

minimizing technical and business risk.

#### REFERENCES

[1] http://acdl.mit.edu/mdo/mdo\_10/INVENT%20M&S%20-%20Wolff.pdf

### **Technical Brief**

## Thermal Packaging From Problem Solver to Performance Multiplier

#### **Avram Bar-Cohen**

Microsystems Technology Office, Defense Advanced Research Projects Agency (DARPA)

**HE INCREASED** integration density of electronic components and subsystems, including the nascent commercialization of 3D chip stack technology, has exacerbated the thermal management challenges facing electronic system developers. The sequential conductive and interfacial thermal resistances associated with the prevailing "remote cooling" paradigm in which heat must diffuse from the active regions on the chip to the displaced coolant, have resulted in only limited improvements in the overall junction-to-ambient thermal resistance of high-performance electronic systems during the past decade. These limitations of Commercial Off-The-Shelf (COTS) thermal packaging are undermining the cadence of Moore's Law and leading to a growing number of products that fail to realize the inherent capability of their continuously improving materials and architecture. Moreover, the uncritical application of this "remote cooling" paradigm, has resulted in electronic systems in which the thermal management hardware accounts for a large fraction of the system volume, weight, and cost and undermines efforts to transfer emerging components to small form-factor applications.

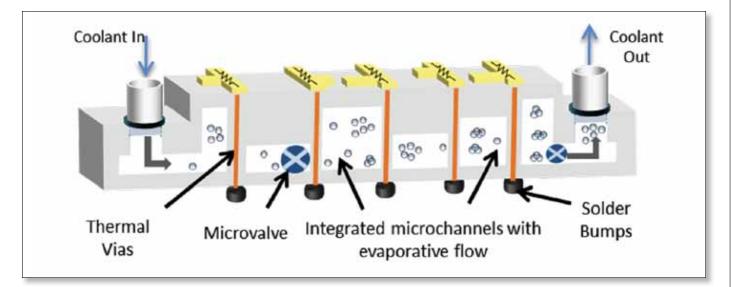

To overcome these limitations and remove a significant barrier to continued Moore's Law progression in electronic components and systems, it is essential to implement aggressive thermal management techniques that directly cool the heat generation sites in the chip, substrate, and/or package. The development and implementation of such "Gen-3" embedded thermal management technology, following on the Gen-1 air-conditioning approaches of the early years and the decades-long commitment to the Gen-2 "remote cooling" paradigm, is the focus of the current DARPA Intra/Inter Chip Enhanced Cooling (ICECool) thermal packaging program. Launched in 2013, ICECool aims to develop and demonstrate "embedded cooling" techniques capable of removing kW/cm<sup>2</sup> chip heat fluxes and kW/cm3 chip stack heat densities, while suppressing the temperature rise of multi-kW/cm<sup>2</sup> sub-mm hot spots [1,2]. The ICECool program is composed of two thrusts: a 3-year ICECool Fundamentals effort, involving several university teams which are developing embedded cooling building blocks and modeling tools, and a 2.5-year ICECool Applications effort, led by several aero-

FIGURE 1: A Cross-Sectional Conceptual Schematic of an Embedded Cooling, Gen-3 (ICECool) device.

sapa:

Shaping the future

## COOLER. FASTER.

### **ALUMINUM EXTRUSIONS MAKE THE DIFFERENCE**

## And Sapa is the largest heat sink extruder in North America, and the world!

Sapa has been providing heat sink extrusions for over 30 years, with 16 manufacturing locations in North America and Thermal Management Centers of Excellence on both coasts that extrude and fabricated finished heat sinks.

The strategic location of production facilities on both coasts means reduced shipping time and cost for thermal management customers, as well as providing centralized expertise for more complex thermal management products through Sapa's North American Technical Center—a research, development, and design center within the company.

In addition, Sapa has developed a new method of manufacturing high ratio air cooled heat sinks. Utilizing our experience in aluminum extrusion combined with Friction Stir Welding technology we're now able to achieve heat sink ratios in excess of 40:1. Our new technique utilizes a modular concept allowing for maximum flexibility in fin geometry, fin ratio, and heat sink footprint. It also allows for the production of large scale heat sinks up to 20" width.

Maximize your product designs with highly efficient thermal management solutions from Sapa Extrusions North America – it's what we like to call **Aluminology**<sup>™</sup>, or the art and science of making aluminum extrusion technology work for you.

## Sapa Extrusions North America

### **MAKING THE CASE**

- ✓ Keep your products cooler longer extruded heat sinks are up to 53% more efficient than aluminum castings.

- ✓ Incredible design flexibility with fin ratios up to 40:1.

- ✓ Nationwide network of production facilities for rapid response to your needs.

877-710-7272 | www.sapagroup.com/NA NorthAmerica.Sales@sapagroup.com space performers and culminating in functional electronic demonstration modules. ICECool performers are pursuing the creation of a rich micro/nano grid of thermal interconnects, using high thermal conductivity, as well as thermoelectric, materials to link on-chip hot spots to microfluidically-cooled microchannels. Such intra/inter chip enhanced cooling approaches are required to be compatible with the materials, fabrication procedures, and thermal management needs of homogeneous and heterogeneous integration in 3D chip stacks, 2.5D constructs, and planar arrays. A conceptual ICECool device is shown in Figure 1.

An intrachip approach would involve fabricating micropores and microchannels directly into the chip [3,4] while an interchip approach would involve utilizing the microgap between chips in three-dimensional stacks [5,6], as the cooling channel. In addition to the inclusion of an appropriate grid of passive and/or active thermal interconnects, it is expected that a combination of intrachip and interchip approaches, linked with thru-silicon and/or "blind" micropores, will confer added thermal management functionality. These microchannels and/or micropores will be integrated into a fluid distribution network, delivering chilled fluid to the chip or package and extracting a mixture of heated liquid and vapor to be transported to the ambiently-cooled radiator.

Some 30 years of thermofluid and microfabrication R&D, driven initially by the publication of the Tuckerman & Pease microchannel cooler paper in 1981 [1] and more recently by compact heat exchanger and biofluidic applications [4,8], has created the scientific and engineering foundation for the aggressive implementation of the "embedded cooling" paradigm. Nevertheless, substantial development and modeling challenges must be overcome if Gen-3 techniques are to supplant the current "remote cooling" paradigm. Successful completion of the DARPA ICECool program requires overcoming multiple microfabrication, thermofluid, and design challenges, including:

- Subtractive and additive microfabrication in silicon, silicon carbide, and synthetic diamond of high aspect ratio, thin-walled microchannels and high aspect ratio micropores; low thermal boundary resistance, high thermal conductivity thermal interconnect grids; on-chip, high power factor, high COP thin-film thermoelectric coolers; and hermetic attachment of liquid supply and liquid/vapor removal tubes.

- Convective and evaporative thermofluid transport in microchannels and micropores- removal of 1 kW/cm<sup>2</sup> chip heat fluxes with 2-5 kW/cm<sup>2</sup> sub-millimeter "hot spots"; low pumping power liquid-vapor manifolds with Coefficients-of-Performance (CoP) between 20 and 30; high-exit-quality, greater than 90%, evaporative flows without flow instabilities and/or local dryout; and high fidelity thermofluid models for single- and two-phase flow in microchannels, microgaps, and micropores.

- Thermal and electrical co-design which moves progressively from passive, thermally-informed designs, which recognize the impact of temperature on functional performance, to active thermal co-design which places functional paths and blocks in the most favorable locations on the chip, to fully-integrated co-design which deals with the impact of

**CLIMATE CONTROL**

### Rittal – The System.

Faster - better - worldwide.

## Thousands of enclosures Hundreds of options Designed and delivered in 10 days

RITTAL

**POWER DISTRIBUTION**

**ENCLOSURES**

FRIEDHELM LOH GROUP

microfluidic channels and thermal interconnects on the electrical design and placement of electrical devices and cells, to mature designs that interactively balance the use of resources to optimize layout for energy consumption and functional performance.

Physics of Failure models that address the failure mechanisms and reliability of the Gen-3 thermal management components, including erosion and corrosion in microchannels, microgaps, and micropores; failure modes induced in the electrically active areas of the chip and/or substrate; and the impact of microfabrication and embedded cooling operation on the structural integrity and stress profile of the microchanneled substrate (intrachip) and/or the chip-to-chip bonding (interchip).

Successful development and implementation of this Gen-3 thermal packaging paradigm would place thermal management on an equal footing with functional design and power delivery, transforming electronic system architecture and unleashing the power of nanofeatured device technology, while overcoming the SWaP (size, weight, and power consumption) bottleneck encountered by many advanced electronic systems. After decades of mere "problem solving" with Gen-1 (HVAC) and Gen-2 (spreaders, heat sinks, and TIMs) thermal management technology, it is expected that widespread adoption of Gen-3 "embedded cooling" techniques will provide a significant performance multiplier for advanced electronic components.

#### REFERENCES

[1] Intrachip/Interchip Enhanced Cooling Fundamentals (ICECool Fun), DARPA BAA 12-50, Posted 7 June 2012.

[2] ICECool Applications (ICECool Apps), DARPA BAA 13-21, Posted 6 February 2013.

[3] D.B. Tuckerman and R.F.W. Pease. "High-performance heat sinking for VLSI." IEEE Electron Device Letters, vol. 2, no. 5, pp. 126–129, 1981.

[4] L.P. Yarin, A. Mosyak and G. Hetsroni. Fluid Flow, Heat Transfer, and Boiling in Micro-Channels. Springer, Berlin, 2009.

[5] A. Bar-Cohen and K.J.L. Geisler. "Cooling the Electronic Brain." Mechanical Engineering, pp. 38–41, April 2011

[6] A. Bar-Cohen, J. Sheehan and E. Rahim. "Two-Phase Thermal Transport in Microgap Channels - Theory, Experimental Results, and Predictive Relations." Microgravity Science and Technology, pp. 1–15, Sept. 2011.

[7] S.Garimella, T. Harirchian, Microchannel Heat Sinks for Electronics Cooling, Volume 1, Encyclopedia of Thermal Packaging, 2013, WSPC, Singapore

**Disclaimer:** The views, opinions, and/or findings contained in this article/presentation are those of the author/presenter and should not be interpreted as representing the official views or policies, either expressed or implied, of the Defense Advanced Research Projects Agency or the Department of Defense.

Distribution Statement A, Approved for Public Release, Distribution Unlimited.

## **Use of JEDEC Thermal Metrics in Calculating Chip Temperatures (without Attached Heat Sinks)**

#### Bruce Guenin

Assoc. Technical Editor

#### INTRODUCTION

**EDEC SINGLE-CHIP** package thermal metrics are widely used as a means of characterizing the thermal performance of semiconductor packages. They correlate the peak temperature of a uniformly-heated semiconductor chip (the junction temperature,  $T_I$ ) with the temperature of a specified region along the heat flow path. The values of these metrics are determined from temperature measurements under standardized conditions, which specify the test method, test board, and thermal environment in rigorous detail [1].

These metrics take the form of an Ohms law resistance calculation. Thermal resistances are calculated using the equation:

$$\Theta_{JX} = \frac{T_J - T_X}{P} \tag{1}$$

where  $T_X$  is the temperature of the region to which the heat is flowing and P is the total power dissipated in the device.

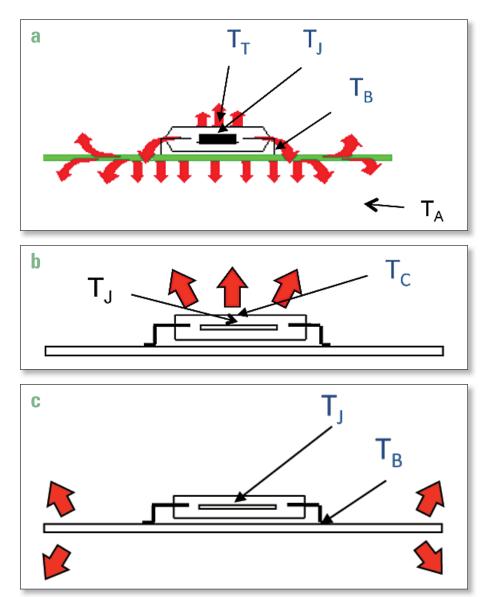

Figure 1 indicates the primary heat flow paths in the four JEDEC-standard test environments: 1) natural convection [2] and forced-convection [3], and the conduction-cooled test environments : 2) junction-to-case [4] and 3) junctionto-board [5].

The junction-to-case and junctionto-board test environments force nearly 100% of the heat to flow along the indicated path.

TThe natural convection and forcedconvection environments bear a closer resemblance to the majority of the end-

**FIGURE 1:** Diagrams representing typical heat flow paths for a package mounted to a test board for the four JEDEC standard test environments: (a) natural and forced convection, (b) junction-to-case, and (c) junction-to-board. The indicated temperature measurement locations are those specified by the respective test standard for each environment.

Got thermal problems? We've got solutions!

- > Read the latest news, standards & product updates

- > Find products & services with our Buyers' Guide

- Download the most recent issue of Electronics Cooling

- > Share & comment on stories with colleagues

electronics-cooling.com

use environments for electronics in comparison with the other two. In these convection-cooled environments, the packages lose a portion of the dissipated heat to the air out of the top surface and the remainder to the board. To a reasonable approximation, for most applications, the two paths account for nearly all of the heat flow out of the package.

There is another class of JEDEC thermal performance metrics that are very useful in calculating junction temperatures for an application environment. They are called thermal characterization parameters and are represented by the Greek letter  $\Psi$  (pronounced "psi") [1]. They are calculated in the same fashion as the theta metrics, as follows:

$$\Psi_{JX} = \frac{T_J - T_X}{P} \tag{2}$$

A key difference between a thermal characterization parameter and a thermal resistance is that, in the case of the former, only part of heat flows to the region represented by the temperature,  $T_X$ . They are useful in estimating  $T_J$ , when  $T_X$  and P are known. The metrics that are most relevant to our purposes here are  $\Psi_{JT}$  and  $\Psi_{JB}$ , where  $T_T$  represents the temperature at the top center of the package and  $T_B$  is the board temperature, measured on a surface trace to which the package is soldered within a 1 mm distance from the edge of the package. The trace should contact the package at the middle of one of its sides.

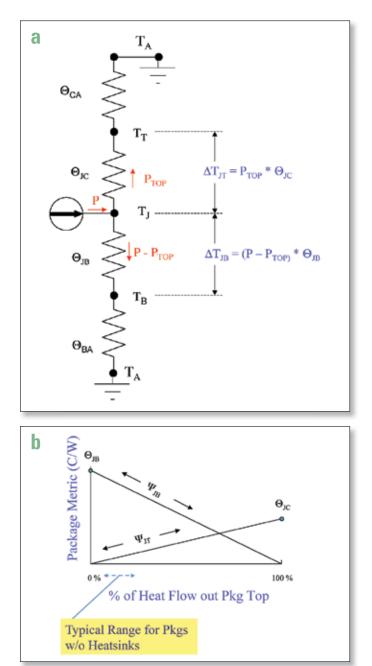

A simple model can be exploited to gain additional insight into the thermal performance of the package/board assembly. Figure 2a represents the two heat flow paths using a simple thermal resistance network. The division of the total heat between these two paths is ultimately determined by the total thermal resistance along each path, which are equal to  $\Theta_{IC}$  +  $\Theta_{CA}$  and  $\Theta_{IB}$  +  $\Theta_{BA}$ , respectively. The resistances  $\Theta_{CA}$  and  $\Theta_{BA}$  represent the efficiency of heat transport from the top of the package and the board, respectively, to the ambient air and are each a function of the air velocity. Unless a heat sink is attached to the top of the package,  $\Theta_{BA}$  will be considerably less than  $\Theta_{CA}$  due to the much larger area of the board surfaces for exchanging heat to the air compared to that of the top of the package. An inspection of this circuit shows that changes in air velocity will modify the values of  $\Theta_{CA}$  and  $\Theta_{BA}$  , leading to changes in the power flowing along the two paths and subsequent changes in  $T_T$  and  $T_B$  and in  $\Psi_{JT}$  and  $\Psi_{JB}$ .

The diagram in Figure 2b illustrates the interrelationship between  $\Psi_{JT}$  and  $\Psi_{JB}$  as the power flowing out the top of the package (P<sub>TOP</sub>) changes. It shows how at small values of P<sub>TOP</sub>, nearly all the power is flowing to the board and  $\Psi_{JB}$  approxi-

mates the value of  $\Theta_{JB}$ . Conversely, if a heat sink is attached to the top of the package, such that  $P_{TOP}$  nearly equals the total power, then  $\Psi_{JT}$  approximates the value of  $\Theta_{JC}$ .

This article explores the relationship of these various metrics and how they can be used 1) with an existing electronic system to estimate the junction temperature or 2) to predict the junction temperature for a system during the design process.

#### BEHAVIOR OF JEDEC THERMAL METRICS IN FORCED AIR TEST ENVIRONMENT

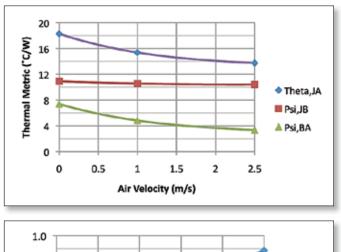

Figure 3a contains a graph of several metrics measured on a 35 x 35 mm, 388 ball, PBGA package with a 4-layer laminate containing two copper planes. The package was mounted to a 100 mm sq. JEDEC-standard board with two copper internal planes. The two upper curves are  $\Theta_{JA}$  and  $\Psi_{JB}$ . A third curve,  $\Psi_{BA}$  was obtained by subtracting  $\Psi_{JB}$  from  $\Theta_{JA}$ .

The  $\Theta_{JA}$  curve displays a significant dependence on the air velocity, primarily due to the role of the board as a fin as it exchanges heat with the convective air flow over its entire area.

In contrast,  $\Psi_{JB}$  is nearly independent of air velocity. This results from the fact that most of the heat flow from the junction flows to the board by way of an internal conduction process. This suggests that  $\Psi_{JB}$  is relatively robust and is an effective measure of the heat conduction efficiency of the package with a relatively small contribution of the convective environment.

The  $\Psi_{BA}$  curve manifests the greatest sensitivity to the air velocity since, by definition, its magnitude is a direct result of the coupled conduction-convection cooling mechanism of the board.

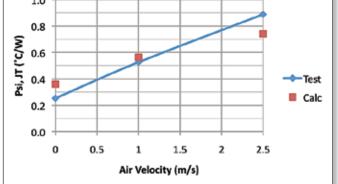

Figure 3b plots  $\Psi_{JT}$  versus air velocity. As expected, it is a sensitive function of air velocity, since the heat flow from the die through the overmolded plastic cap is proportional to the heat transfer coefficient associated with a certain air flow velocity. One notes also that at air velocities up to 2.5 m/s,  $\Psi_{JT}$ is less than 1 °C/W. The implication of this is that for modest power levels, the temperature of the top center of the package is only slightly cooler than the junction. This serves to reduce the error in calculating T<sub>J</sub> since the value of  $\Delta T_{JT}$  calculated using Eqn. 2 would then be a very small correction to add to the much larger measured value of T<sub>T</sub>.

This analysis leads to the conclusion that the main value of  $\Psi_{JB}$  is that it is moderately robust and can be used to predict the temperature difference between the junction and a board, when the dissipated power is known. Conversely  $\Psi_{JT}$  is more useful if one has an operating electronic system in front of him and wants to know the die temperature in a plastic package by a measurement of the temperature at the top of the package.

It is not always the case that  $\Psi_{\rm JT}$  is provided by the package vendor. In this situation, it is relatively easy to calculate it.

In a previous column, the following equation was derived [6]:

$$\Psi_{JT} = \frac{h \Theta_{JA} t_{EMC}}{\kappa_{EMC}}$$

(3)

where h is a value of heat transfer coefficient calculated at the air velocity of interest, and  $t_{EMC}$  and  $\kappa_{EMC}$  are the thickness

**FIGURE 2:** (a) Thermal resistor network representing junction-to-boardto-air path and junction-to-case-to-air path. (b) Diagram illustrating the relationship between  $\Theta$  and equivalent  $\Psi$  values as a function of heat flow out of the top of the package to air.

of the epoxy mold compound above the die and its thermal conductivity. In the present example,  $t_{_{EMC}}$  and  $\kappa_{EMC}$  are 0.86 mm and 0.7 W/mK, respectively.

The calculated values of  $\Psi_{JT}$  are plotted in Figure 3b and are also listed in the Table along with the remaining parameters input into Eqn. 3. The differences between the measured and calculated values of  $\Psi_{JT}$  are small in absolute terms.

#### USING $\Psi_{\text{JB}}$ is to predict junction temperature in a design

In order to successfully use the  $\Psi_{JB}$  metric in predicting the junction temperature, one needs to know  $T_B$  and the dissipated power and air flow conditions in the application.

There are numerous methods available for getting an estimate of  $T_B$ . Among the options is to build a load board, having the overall dimensions and conductivity of the actual board and applying the expected heat loads using heaters and also an appropriate cooling method [7]. Alternatively, one could create either an appropriate computational fluid dynamics (CFD) or finite element or finite difference conduction model of the board and accounting for the heat loads and cooling. Lastly, if a quick and moderately accurate solution is needed, it is possible to estimate the board temperature by including a single-package board in the model. The appropriate board size would be determined by taking the area of the actual board and multiplying by the ratio of the power of the device of interest to the total power due to all the devices on the board [8].

The usefulness of  $\Psi_{JB}$ , which is generated in a standard test environment, to the prediction of junction temperatures in an application results from the fact that in both environments, there is a convective boundary condition applied to the top of the package, which, ideally, would be at the same air velocity.

In general, a single resistance link from the die to the top of the package is not consistently accurate for an arbitrary boundary condition. To have robust boundary condition independence requires a compact thermal model, for example [9].

The initial work devoted to the development of the  $\Psi_{JB}$  standard showed similar values for a given package whether it was tested on JEDEC-standard multilayer boards or on an application board [10].

#### CONCLUSIONS

The JEDEC-standard thermal characterization parameters,  $\Psi_{JB}$  and  $\Psi_{JT}$ , can be valuable in facilitating the calculation of the junction temperature in a semiconductor package both for a live system and also in a predictive calculation. These metrics, determined by measurement, complement a purely thermal simulation approach by providing convenient experimental validation of simulated junction temperatures.

FIGURE 3: Thermal test results versus air velocity for a 35 x 35 mm, 388 ball, PBGA package having a 4-layer laminate attached to a 4-layer JEDEC-standard board.

#### REFERENCES

JEDEC Standard JESD51-12, "Guidelines for Reporting and Using Electronic Package Thermal Information." All JEDEC standards are available for download at no charge from www.jedec.org.

JEDEC Standard JESD51-2A, "Integrated Circuits Thermal Test Method Environmental Conditions - Natural Convection (Still Air)."

[3] JEDEC Standard JESD51-6, "Integrated Circuit Thermal Test Method Environmental Conditions - Forced Convection (Moving Air),"

[4] JEDEC Standard JESD51-14, "Transient Dual Interface Test Method for the Measurement of the Thermal Resistance Junction to Case of Semiconductor Devices with Heat Flow Through a Single Path."

[5] JEDEC Standard JESD51-8, "Integrated Circuit Thermal Test Method Environmental Conditions — Junction-to-Board."

> [6] B. Guenin, "Determining the Junction Temperature in a Plastic Semiconductor Package, Part I," ElectronicsCooling, Vol. 5, No. 2, May, 1999.

> [7] B. Siegal, "Thermal Load Board Design Considerations," ElectronicsCooling, Vol. 18, No. 3, September, 2009.

[8] B. Guenin, "Characterizing a Package on a Populated Printed Circuit Board," ElectronicsCooling, Vol. 7, No. 2, May, 2001.

[9] S. Shidore, "Compact Thermal Modeling in Electronics Design" ElectronicsCooling, Vol. 13, No. 2, May, 2007.

[10] B. Joiner "Use of Junction-to-Board Thermal Resistance in Predictive Engineering," Electronics Cooling, Vol. 5, No. 1, January, 1999.

| TABLE: COMPARISON OF CALCULATEDAND MEASURED VALUES OF $\Psi_{JT}$ |                     |                    |                  |                         |

|-------------------------------------------------------------------|---------------------|--------------------|------------------|-------------------------|

| 35mm, 388 ball PBGA pkg, 4-Layer laminate on 4-Layer board        |                     |                    |                  |                         |

| Vair                                                              | h                   | $\Theta_{JA}$ Test | $\Psi_{JT}$ Calc | $\Psi_{\text{JT}}$ Test |

| m/s                                                               | W/m <sup>2</sup> -K | C/W                | C/W              | C/W                     |

| 0                                                                 | 16                  | 18.3               | 0.36             | 0.25                    |

| 1                                                                 | 30                  | 15.3               | 0.56             | 0.53                    |

| 2.5                                                               | 44                  | 13.7               | 0.74             | 0.89                    |

## Keep Your Optics Clear, Gap Filler 1500LV Offers Over 10x Reduction In Outgassing.

Headlight assembly with a standard thermal interface material

Headlight assembly with new Bergquist Gap Filler I500LV

#### **Bergquist Gap Filler 1500LV supports greater clarity inside sensitive electronic applications where fogging of lenses or optics from outgassing is a consideration.**

## Control outgassing, improve thermal performance for a clearer environment.

Gap Filler 1500LV is a low volatility, twocomponent, liquid-dispensable thermal interface material. This ultra conformable elastomer provides a thermal conductivity of 1.8 W/m-K. It offers the high temperature resistance and low

modulus of a silicone material, with significantly lower levels of outgassing. At higher temperatures, volatiles from outgassing can create issues in enclosed fixtures such as lighting where the clarity is crucial. Gap Filler I 500LV is ideal for use in these lighting applications or other situations where fogging of lenses or optics is a potential consideration.

#### Low assembly stress on electronic components.

952.835.2322

Gap Filler I500LV is thixotropic and although it will remain in place after dispensing, the material will flow easily under minimal pressure resulting in little to no stress on fragile components during assembly.

www.bergquistcompany.com 1.800.347.4572

Gap Filler I500LV cures at room temperature – and the curing process can be accelerated with the addition of heat. When cured, this material provides a soft, thermally conductive, form-in-place elastomer that is ideal for filling unique and intricate air voids and gaps.

#### Another innovative thermal solution for optimized dispensing.

Gap Filler I500LV is just one of an expanding line of liquid dispensed materials. Unlike precured gap filling materials, liquid dispensed materials offer infinite thickness options and eliminate the need for specific pad thicknesses or die-cut shapes for individual applications. Applying precise amounts of material directly to the target surface results in an effective use of material with minimal waste.

To qualify for your FREE Gap Filler 1500LV Kit, call or visit our website: www.bergquistcompany.com/nofog

18930 West 78th Street • Chanhassen, Minnesota 55317

fax 952.835.0430

**Thermal Materials • Thermal Substrates • Fans and Blowers**

## **Thermal Management of Many-Core Processors** using Power Multiplexing

#### Man Prakash Gupta, Satish Kumar

power). This brings new opportunities

for the dynamic thermal management

(DTM) techniques, and their role

to address the challenges of power

dissipation in many-core processors

becomes very important. Many DTM

techniques have been explored such as

clock gating, dynamic voltage and fre-

quency scaling, and thread migration

for single and multi-core processors

[6-9]. All these reactive methods can

have power and performance overhead

apart from the hardware and software

proactive method can be utilized as

a supplementary approach to the re-

active methods for effective thermal

management of many-core processors

[10, 11]. Power multiplexing technique

involves redistribution (or migration)

Power multiplexing which is a

implications.

G. W. Woodruff School of Mechanical Engineering, Georgia Institute of Technology

#### INTRODUCTION

**UE TO THE** growing demands of higher performance and faster computing, the number of cores in a microprocessor chip has been increasing consistently. The transition from single core to multicore technology has already been observed in the past few years and with the strong potential of parallel computing, the transition from multicore to many-core is also imminent where the number of cores on a single chip is expected to reach in hundreds or even thousands per single processor die. Such large-scale integration and very high power densities on chip will bring a significant challenge of heat dissipation. The traditional aircooling methods begin to reach their flow and acoustic limits for very high power density (~1.5 W/mm<sup>2</sup>) apart from being inefficient from economic point of view when applied to manycore technology [1, 2]. Moreover, the uneven workload on the cores leads to spatiotemporal non-uniformity in the thermal field on chip which can be detrimental to its performance and reliability [3]. The leakage power also increases exponentially with temperature resulting in higher power dissipation, and cooling costs [4, 5].

Another way to obtain a uniform on-chip temperature distribution and lower peak temperature is efficient redistribution of heat within the chip which can help to improve the energy efficiency and coefficient of performance (~compute/cooling

**Man Prakash** is a Ph.D. candidate in the department of Mechanical Engineering at Georgia Tech. He received his B.Tech. - M.Tech. dual degree in mechanical engineering from Indian Institute of Technology Kanpur, India in May 2009. His current research work is related with thermal management of microelectronics devices and electro-thermal transport in carbon nanotube based composites.

**Dr. Satish Kumar** joined Georgia Tech in 2009 as an Assistant Professor in the George W. Woodruff School of Mechanical Engineering. Prior to joining Georgia Tech, he worked at IBM Corporation where he was responsible for the thermal management of electronic devices. Kumar received his Ph.D. in mechanical engineering and M.S. degree in electrical and computer Engineering from Purdue University, West Lafayette in 2007. He received his M.S. degree in mechanical engineering from Louisiana State University, Baton Rouge in 2003 and B.Tech. degree in mechanical engineering from the Indian Institute of Technology, Guwahati in 2001. His research interests are in thermal management, thermo-electric coolers, electro-thermal transport in carbon nanotube, graphene and 2D materials based flexible-electronics. He is author or co-author of over 65 journal or conference publications.

#### of the workload of the cores in the chip at regular time intervals to control the thermal profile on the chip. This approach is different from the reactive DTM techniques which wait for the temperature to increase beyond a certain threshold value. The idea is to improve the thermal profile by using idle or underutilized cores efficiently. The guiding rule which governs the redistribution of workload is called migration policy. The time interval at which this migration takes place is referred to as timeslice. A smaller timeslice corresponds to faster multiplexing. The value for the timeslice is typically chosen such that it is smaller than the characteristics thermal time constant $(\tau)$ of the system. In

the present case, this time constant

interference technology

Find solutions at interferencetechnology.com

SUBSCRIBE

EMC ZONE . LATEST BLOC POSTS

eder Plus Test #

$\tau$  is defined as the time for the chip peak temperature to reach 63% of the steady-state after turning on the power under flow conditions described below. The value of  $\tau$  is estimated to be 0.1 s. This criterion for the timeslice selection is based on the requirement that the 2D effects of power multiplexing need to be realized faster than the 3D thermal diffusion in order to get full advantage of multiplexing. A tile-type homogeneous 256-core processor is considered where the cores are arranged in a 16x16 2D array [12]. The power dissipation value has been selected based on the prediction by International Technology Roadmap of Semiconductor (ITRS) for 16 nm node technology. The model considers 2 W of power dissipation in each active core which is reasonable for cores with 16 nm node technology running at 3 GHz. The total power dissipation on the chip is considered to be 128 W, i.e., at one instant only 25% cores (~64 cores) are active.

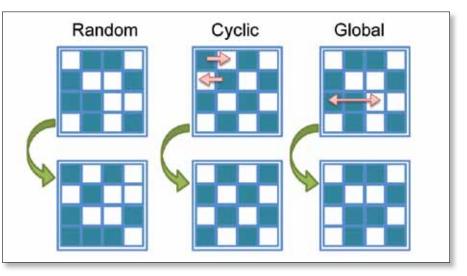

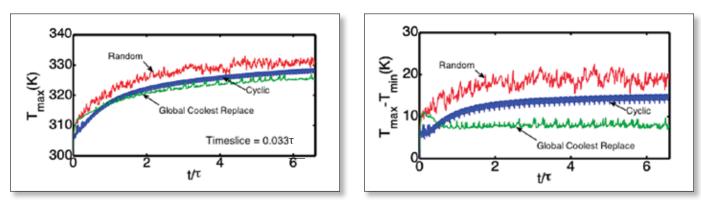

Three migration policies namely, random, cyclic and global policies are explored here (Figure 1). Random policy involves random redistribution of all active cores at each timeslice. In cyclic policy active cores are assigned in a checkerboard configuration and shifted in a circular fashion at each timeslice maintaining checkerboard configuration. Global policy involves the swapping of workload between hottest and coolest cores at regular time intervals.

#### **METHODOLOGY AND RESULTS**

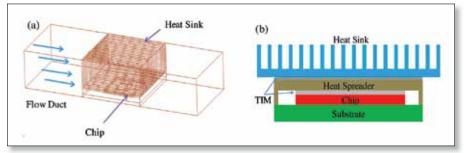

Using computational fluid dynamics (CFD), a detailed heat transfer analysis of the electronic package is performed. The computational domain is comprised of a flow duct, a

heat sink, a heat spreader, the thermal interface material (TIM), a chip and a substrate (Figure 2) [12]. The properties of the various components of the system are considered to be constant and are listed in Table 1. It should be noted that temperature dependent thermal conductivity of the components does not cause any significant change in the results since the temperature variation is between 300 and 330 K only. The dimensions of chip are 12 mm x 0.5 mm x 12 mm and the typical size of a grid cell inside chip is 0.375

**FIGURE 1:** Illustration of the migration policies for power multiplexing on many-core processors. Random multiplexing involves arbitrary exchange of workloads among all cores at regular time intervals. Cyclic multiplexing policy preserves checkerboard configuration during multiplexing. Global policy involves exchange of workload between hottest and coolest cores.

**FIGURE 2: (a)** Flow duct with a heat sink and an electronic package used for the thermal modeling. **(b)** Schematic of the heat sink and electronic package of the many-core processor which include heat spreader, thermal interface material (TIM), chip and substrate (view along the direction of inlet flow).

| TABLE 1: MATERIAL PROPERTIES OF THE COMPONENTS<br>OF CHIP PACKAGE |          |              |               |                 |

|-------------------------------------------------------------------|----------|--------------|---------------|-----------------|

| Component                                                         | Material | ρ<br>(kg/m³) | Cp<br>(J/kgK) | Value<br>(W/mK) |

| Heat Sink                                                         | copper   | 8978         | 381           | 387.6           |

| Heat Spreader                                                     | aluminum | 2719         | 871           | 202.4           |

| TIM                                                               | grease   | 2550         | 700           | 4               |

| Chip                                                              | silicon  | 2330         | 712           | 141.2           |

mm x 0.1mm x 0.375mm. A uniform velocity profile at the inlet of the air flow tunnel is considered with constant velocity of 5 m/s. An outflow boundary condition is imposed at the outlet of the tunnel and no-slip boundary condition is imposed at the walls of the tunnel and outer surfaces of the electronic package (Figure 2 (a)). The flow inside the tunnel is turbulent as Reynolds number based on the inlet flow rate and duct hydraulic diameter width is 20,000. As accurate turbulent flow computations are not critical in

the present study, Spalart-Allmaras turbulence model [13] was used, which is a simple one-equation model and appropriate for applications involving wall-bounded flows and for avoiding fine meshing near the wall. We consider SIMPLE scheme for pressurevelocity coupling, implicit scheme for transient formulation and second order upwind scheme for the discretization of all governing equations [14].

Three cases (slow, fast or no multiplexing) are investigated corresponding to each migration policy to examine the effect of timeslice variation. For random power multiplexing, results suggest faster multiplexing (at timeslice =  $0.0033 \tau$  which equals to  $10^6$ clock cycles) provides  $10^{\circ}$ C reduction in the peak temperature ( $T_{max}$ ) and  $15^{\circ}$ C reduction in the maximum spatial temperature difference ( $T_{max}-T_{min}$ ) [12]. A graphic comparison of the thermal

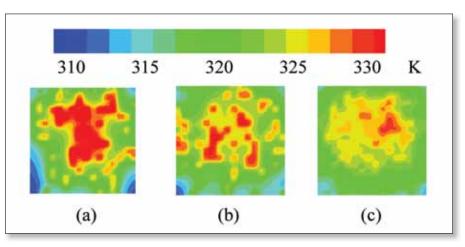

**FIGURE 3:** Thermal profile on 256 core chip at time instant,  $t/\tau = 6.6$ , for **(a)** no multiplexing, **(b)** slow multiplexing with timeslice =  $0.033\tau (10^7 \text{ clock cycles})$ , and **(c)** fast multiplexing with timeslice =  $0.0033\tau (10^6 \text{ clock cycles})$  with random core migration policy. 25% active cores with total power = 128W.

FIGURE 4: Comparison of the effect of different migration policies on (a) peak temperature, (b) spatial temperature difference. Timeslice is kept as 0.033τ during power multiplexing. 25% cores are considered to be active with total power = 128W.

profile on the chip at time instant,  $t = 6.6 \tau$ , is shown in Figure 3.

For cyclic policy, results indicate that it reduces the peak temperature by only 3°C even for vary fast multiplexing. This small reduction can be attributed to the pre-existing checkerboard configuration of active cores. The maximum spatial temperature difference across the chip is however significantly reduced (by 7°C).

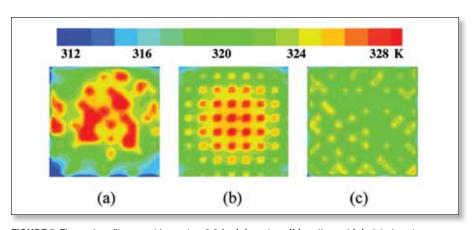

Global policy is intrinsically different from the previous two policies as it takes decisions based on the instantaneous chip temperature and also, fewer cores are involved in the multiplexing. To begin with, only a pair of cores is considered for the global multiplexing, *i.e.*, the workload is swapped between the hottest and the coolest core at each timeslice. It is found that global policy shows significant improvement in thermal profile even for very slow multiplexing. Analysis of the power map at each migration step, finds that the global coolest policy ingeniously places the active cores away from the center of the chip such that it not only reduces peak temperature by a significant amount but also reduces thermal non-uniformity. By comparison

#### SUMMARY

Power multiplexing approach has been presented as a prospective thermal management technique for many-core processors. The global power multiplexing has been found to be the most effective among the three policies discussed in this article. The peak temperature reduction of 10°C and the maximum spatial temperature difference reduction of

20°C have been observed on a 256-core chip using global policy based power multiplexing. This can be attributed to its inherent approach to optimize the proximity of active cores on a finite size chip by automatically considering the effect of geometrical and thermal properties of the 3D system through the temperature distribution at each migration step. The work presented in this article may be considered as a first order analysis of migration policies as simple policies are applied in case of the homogeneous many-core processors. More evolved policies can be formulated to handle thermal management of heterogeneous manycore processors.

**FIGURE 5:** Thermal profile on a chip at  $t/\tau = 6.6$  for **(a)** random, **(b)** cyclic, and **(c)** global coolest replace policies. Timeslice is taken as  $0.033\tau$ . Very high spatial thermal uniformity can be seen for the global multiplexing. 25% active cores with total power = 128W.

#### REFERENCES

[1] J. Michael J. Ellsworth, "High Powered Chip Cooling - Air and Beyond," Electronics Cooling, 2005.

[2] P. Zhou, J. Hom, G. Upadhya, K. Goodson, and M. Munch, "Electro-kinetic microchannel cooling system for desktop computers," Twentieth Annual IEEE Semiconductor Thermal Measurement and Management Symposium, Proceedings 2004, pp. 26-29, 2004.

[3] R. Mukherjee and S. O. Memik, "Physical Aware Frequency Selection for Dynamic Thermal Management in Multi-Core Systems," in IEEE/ACM International Conference on Computer-Aided Design (ICCAD)., 2006, pp. 547-552.

[4] M. Janicki, J. H. Collet, A. Louri, and A. Napieralski, "Hot spots and coreto-core thermal coupling in future multi-core architectures," in 26th Annual IEEE Semiconductor Thermal Measurement and Management Symposium (SEMI-THERM)., 2010, pp. 205-210.

[5] E. Kursun and C. Chen-Yong, "Temperature Variation Characterization and Thermal Management of Multicore Architectures," IEEE Micro., vol. 29, pp. 116-126, 2009.

[6] D. Brooks and M. Martonosi, "Dynamic thermal management for high-performance microprocessors," in The Seventh International Symposium on High-Performance Computer Architecture (HPCA)., 2001, pp. 171-182.

[7] P. Chaparro, J. Gonzalez, G. Magklis, Q. Cai, and A. Gonzalez, "Understanding the Thermal Implications of Multi-Core Architectures," IEEE Transactions on Parallel and Distributed Systems, vol. 18, pp. 1055-1065, 2007.

[8] V. Hanumaiah, S. Vrudhula, and K. S. Chatha, "Maximizing performance of thermally constrained multi-core processors by dynamic voltage and frequency control," in IEEE/ACM International Conference on Computer-Aided Design

Digest of Technical Papers (ICCAD)., 2009, pp. 310-313.

[9] R. Rao, S. Vrudhula, and C. Chakrabarti, "Throughput of multi-core processors under thermal constraints," in ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED). , 2007, pp. 201-206.

[10] C. Y. Cher and E. Kursun, "Exploring the Effects of On-Chip Thermal Variation on High-Performance Multicore Architectures," ACM Transactions on Architecture and Code Optimization, vol. 8, Apr 2011.

[11] M. K. Cho, C. Kersey, M. P. Gupta, N. Sathe, S. Kumar, S. Yalamanchili, and S. Mukhopadhyay, "Power Multiplexing for Thermal Field Management in Many-Core Processors," IEEE Transactions on Components Packaging and Manufacturing Technology, vol. 3, pp. 94-104, Jan 2013.

[12] M. P. Gupta, M. K. Cho, S. Mukhopadhyay, and S. Kumar, "Thermal Investigation Into Power Multiplexing for Homogeneous Many-Core Processors," Journal of Heat Transfer-Transactions of the ASME, vol. 134, Jun 2012.

[13] P. Spalart and S. Allmaras, "A one-equation turbulence model for aerodynamic flows," American Institute of Aeronautics and Astronautics, vol. Technical Report AIAA-92-0439 1992.

[14] S. V. Patankar, Numerical heat transfer and fluid flow / Suhas V. Patankar.

Washington : New York :: Hemisphere Pub. Corp. ; McGraw-Hill, 1980.

## **Characterization of Server Thermal Mass**

#### Mahmoud Ibrahim Panduit

Heat sink top measurement Heat sink top measurement Heat sink top measurement Heat sink top measurement Heat sink top measurements Heat s

**Mahmoud Ibrahim** is a senior analysis engineer at Panduit Corporation, working on advanced energy-efficient cooling controls and technologies for data centers. He received his PhD in Mechanical Engineering from Binghamton University in 2012. He is a member of ASME, and ASHRAE. He has authored and co-authored over 20 technical publications in journals, conferences, and book chapters.

#### **HE CONTINUOUS** growth

of internet business and social media is necessitating the construction of new data centers to support the rising vol-

ume of internet traffic. This is in addition to the increasing number of colocation facilities being built to support different business sizes with different functions. Generally, data centers are considered mission critical facilities that house a large number of electronic equipment, typically servers, switches, and routers that demand high levels of electrical power which eventually dissipates as heat. These facilities require a tightly controlled environment to ensure the reliable operation of the IT equipment. In many cases, with the IT equipment being a core player in the customer-business relationship regardless of the sole function of the business (healthcare, finance, social media, etc.), facility managers and data center operators tend to unnecessarily overcool their data centers fearing the presence of hotspots within the facility. This explains why in the 2007 EPA report to Congress it was estimated that U.S. data centers used 61 billion kWh of electricity in 2006, representing 1.5% of all U.S. electricity consumption and double the amount consumed in 2000 [1]. Consequently, data center cooling technology has gained considerable research focus over the past few years in an effort to lower these high levels of energy consumption.

Dynamic cooling has been proposed as one approach for enhancing the energy efficiency of data center facilities. It involves using sensors to monitor continuously the data center environment and making real time decisions on how to allocate the cooling resources based on the location of hotspots and concentration of workloads. In order to effectively implement this approach, it is vital to know the transient thermal response of the various systems comprising the data center, which is a function of thermal mass.

Another crucial requirement for mission critical facilities, in addition to providing adequate cooling to IT equipment, is securing constant electrical power supply. A survey conducted by Ponemon Institute on data center outages [2] stated that 88% out of 453 surveyed data center operators experienced a loss of primary utility power and hence the power outage of their data centers, with an average of 5.12 complete data center outages every two years. When an outage occurs, it is standard practice to continue to furnish power to the servers using uninterruptable power supplies (UPSs) for a period of time. This allows the fans in the server to continue to operate while allowing sufficient time for the server to attempt a controlled shutdown. However, without active cooling the ambient air temperature within the data center will rise. How quickly the data center environment reaches the critical limit of the IT equipment is once again a function of thermal mass. A number of studies have addressed this issue and developed simple energy based models to predict the data center room temperature rise during power failure [3-4]. While such models may provide useful information, they are based on combining all parameters in the data center into one, so as to provide an overall sense of the thermal response. These models however are not capable of providing a detailed view of the data center whether during dynamic cooling control or during power failure. In order to do so, the thermal mass of the various objects present in the data center must be determined.

This article introduces an experimental technique used to extract the thermal mass of servers, which can further be used as a compact model embedded in Computational Fluid Dynamics (CFD) simulations for data center level analyses, or analytical based thermal models. All the experimental testing and results presented are conducted on a typical 2U server used in the market.

#### **APPROACH**

In order to obtain a thermal mass of the server, the following energy balance equation is applied:

$$\dot{Q} = (\dot{m}c_p)_{air}\Delta T_{air} + (pVc_p)_{unit} \frac{\partial T_{unit}}{\partial T} \quad \textbf{(1)}$$

where  $\dot{Q}$  is the total energy generated by the server per unit time,  $\dot{m}$ is the air mass flow rate within the server, and  $(pVc_p)_{unit}$  is the thermal mass of the server. The first term on the right-hand side of Equation 1 represents forced convection cooling by the server fans, with the second term accounting for the server thermal storage. Measuring the air velocity inside the server, the power consumed, the air temperature rise  $(\Delta T_{air})$  across the server and a repre-

sentative temperature of the server with time, one can extract the thermal mass. Although it appears straightforward since all the variables are measured, obtaining a server unit temperature  $T_{unit}$  poses difficulties that require further assumptions.

Given that the server is comprised of numerous components, obtaining an appropriate average temperature of the unit as a whole requires a weighted allocation of the individual components. The major components that may have an effect on the average unit temperature are CPU/heat sink assemblies, hard disk drives, graphic card, memory modules, fans, power supply unit, and the chassis including the motherboard. The primary materials used in the production of these various components are aluminum, steel, copper, and silicon. Knowing that the

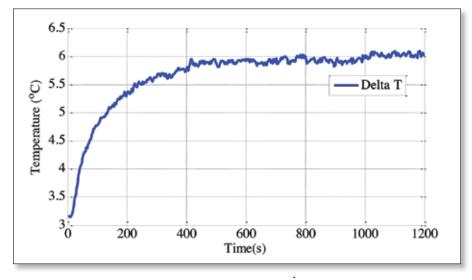

**FIGURE 2:** Measured air temperature rise ( $\Delta T$ ) across the server at Q of 350 W.

specific heat capacity of the above materials within the range of 0.5-0.9 KJ/kg.K, and that the range of heat capacity for condensed matter is 1-4 J/m<sup>3</sup>.K [5], one can assume that the contribution of each component to the unit temperature will be solely determined by the ratio of the component weight to the overall server weight. By obtaining the weights of the various server components, the percentage contribution of each component to the overall unit temperature can be computed. The unit temperature is then calculated by multiplying each component's percentage by its measured temperature as represented by Equation (2). The equation coefficients represent the relative mass of each component.

$$T_{unit} = 0.03 T_{fans} + 0.05 T_{GC} + 0.07 T_{HDD}$$

(2)

+0.04  $T_{RAM} + 0.08 T_{PS} + 0.11 T_{CPU/HS} + 0.61 T_{Chassis}$

#### **TEST SETUP**

The server was located in a large room to insure a uniform inlet ambient air temperature, not affected by the server exhaust temperature. Type J thermocouples with a measurement uncertainty of ±1.1°C, and a thermal response time of less than 1 second were used for temperature measurement. The thermocouples were attached in various locations to measure temperatures of the different components within the server, as well as the air intake and exhaust temperatures (Figure 1). The thermocouples were attached using a thermal adhesive tape to obtain the best possible thermal contact. A data acquisition (DAQ) unit was used to

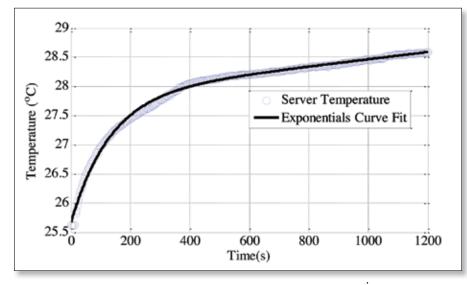

**FIGURE 3:** Curve fit of the calculated server transient temperature profile ( $T_{unit}$ ) at  $\dot{Q}$  of 350 W.

log the temperature data. A power meter was used to measure the power consumed by the server with an accuracy of  $\pm 1\%$  and a response time less than 5 seconds.

In addition to the thermocouples, the server is equipped with sensors from the manufacturer, taking temperature measurements of different components, as well as measuring the four CPU fans' speed. Software was installed to log the reported fan speed measurements and temperature measurements by the various components in the server. Data was collected every three seconds, and it was synchronized between the three sources: power meter, DAQ unit, and server sensors using the clocks on each computer.

Fig. 1 shows a top view of the server, highlighting where the thermocouples were placed. Fourteen thermocouples were used to obtain an average server air outlet temperature, so as to account for the large variation in outlet temperature across the width of the server.

Through operating the server at a specific power level and measuring the corresponding temperatures, fan speeds, and power consumption, one can extract the server thermal mass using Equation (1). Various power levels were tested to ensure the validity and accuracy of the approach. All the tests were conducted in an identical manner, where the server was operated initially at idle state and the temperature measurements were used to determine a steady state operation. Steady state condition was determined by observing that the server air exhaust temperatures as well as the component surface temperatures remained constant  $(\pm 0.5^{\circ}C)$  for at least 10 minutes. A computational load is applied to the server to run it at a specific power level causing component surface temperatures and server exhaust temperature to increase. Loads applied to the server varied from 220W to 350W while the fan airflow was kept constant. Once a steady state is reached, computations are terminated allowing the server to go back to its idle state.

#### RESULTS