# **Gelectronics COLING**

#### FEATURED IN THIS EDITION

27 ASHRAE TECHNICAL COMMITTEE 9.9:

MISSION CRITICAL FACILITIES, DATA

CENTERS, TECHNOLOGY SPACES,

AND ELECTRONIC EQUIPMENT

33 JEDEC THERMAL STANDARDS: DEVELOPING A COMMON UNDERSTANDING

38 HEAT SPREADER EFFICIENCY

IMPROVEMENTS BY ADDITION OF

LATENT HEAT SOLUTION MATERIALS

THERMAL MANAGEMENT

10 THERMAL LIVE 2019 TECHNICAL PROGRAM

18 THERMAL FACTS & FAIRY TALES

LARGER ERRORS WITH SMALLER STUFF

**20 CALCULATION CORNER**THERMAL INTERACTIONS BETWEEN HIGH-POWER PACKAGES AND HEAT SINKS, PART 2

25 TECHNICAL BRIEF

SUMMARY OF THE IEEE ITHERM

2019 CONFERENCE

44 2020 SEMI-THERM® TECHNICAL PROGRAM

© Copyright 2019 Electronics Cooling

## **Liquid Cooling Solutions**

Professionally designed, built and tested to withstand harsh environments

- High performance Coolant Distribution Unit (CDU)

- Impinging cold plate design with lower pressure drop

- Broad range of testing equipment to ensure product quality and performance

- Micro-channel cold plate block designs

- Liquid direct cooling for memory DIMMs

- High-grade tubing with low permeation, high-pressure capacity and small bending radii achievable

- Hot-swappable quick-disconnect capability for dry disconnect

# CONTENTS

# **G**electronics COOLING

www.electronics-cooling.com

#### 5 EDITORIAL

Bruce Guenin

#### 7 COOLING EVENTS

News of Upcoming Thermal Management Events

#### 10 THERMAL LIVE™ 2019 TECHNICAL PROGRAM

#### **18 THERMAL FACTS AND FAIRYTALES**

Larger Errors with Smaller Stuff Ross Wilcoxon

#### **20 CALCULATION CORNER**

Thermal Interactions Between High-Power Packages and Heat Sinks, Part 2

Bruce Guenin

#### **25 TECHNICAL BRIEF**

Summary of the IEEE ITherm 2019 Conference John F. Maddox

#### **27 FEATURE ARTICLE**

ASHRAE Technical Committee 9.9: Mission Critical Facilities, Data Centers, Technology Spaces, and Electronic Equipment Dustin Demetriou

#### **33 FEATURE ARTICLE**

JEDEC Thermal Standards: Developing A Common Understanding Jesse Galloway

#### 38 FEATURE ARTICLE

Heat Spreader Efficiency Improvements by Addition of Latent Heat Solution Materials

Mark Hartmann

#### **43 TECHNICAL EDITORS SPOTLIGHT**

#### 44 2020 SEMI-THERM® TECHNICAL PROGRAM

#### **50 INDEX OF ADVERTISERS**

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, or stored in a retrieval system of any nature, without the prior written permission of the publishers (except in accordance with the Copyright Designs and Patents Act 1988).

The opinions expressed in the articles, letters and other contributions included in this publication are those of the authors and the publication of such articles, letters or other contributions does not necessarily imply that such opinions are those of the publisher. In addition, the publishers cannot accept any responsibility for any legal or other consequences which may arise directly or indirectly as a result of the use or adaptation of any of the material or information in this publication.

ElectronicsCooling is a trademark of Mentor Graphics Corporation and its use is licensed to Lectrix. Lectrix is solely responsible for all content published, linked to, or otherwise presented in conjunction with the ElectronicsCooling trademark.

#### **PUBLISHED BY**

Lectrix

1000 Germantown Pike, F-2 Plymouth Meeting, PA 19462 USA Phone: +1 484-688-0300; Fax:+1 484-688-0303 info@lectrixgroup.com www.lectrixgroup.com

#### **CHIEF EXECUTIVE OFFICER**

Graham Kilshaw | Graham@lectrixgroup.com

#### **VP OF MARKETING**

Geoffrey Forman | Geoff@lectrixgroup.com

#### **EDITORIAL DIRECTOR**

Jennifer Hooker | Jennifer@lectrixgroup.com

#### **CREATIVE DIRECTOR**

Chris Bower | Chris@lectrixgroup.com

#### **VP OF STRATEGIC DEVELOPMENT**

Ian Quinn | Ian@lectrixgroup.com

#### BUSINESS DEVELOPMENT DIRECTOR

Janet Ward | Jan@lectrixgroup.com

#### PRODUCTION COORDINATOR Jessica Stewart | Jessica@lectrixgroup.com

sessica stemart | sessica@ieetrixgroup.com

#### LEAD GRAPHIC DESIGNER

Kristen Tully | Kristen@lectrixgroup.com

#### PRODUCTION ARTIST

Noah Sneddon | Noah@lectrixgroup.com

#### **CONTENT MARKETING MANAGER**

Danielle Cantor | Danielle@lectrixgroup.com

#### ADMINISTRATIVE MANAGER

Eileen Ambler | Eileen@lectrixgroup.com

#### ACCOUNTING ASSISTANT

Susan Kavetski | Susan@lectrixgroup.com

#### ASSOCIATE TECHNICAL EDITORS

Victor Chiriac, Ph.D, ASME Fellow

Principal Architect Huawei R&D USA vchiriac@cox.net

#### Bruce Guenin, Ph.D.

Consultant

San Diego, CA

sdengr-bguenin@usa.net

#### Genevieve Martin

R&D Manager, Thermal & Mechanics Competence Signify genevieve.martin@signify.com

#### Ross Wilcoxon, Ph.D.

Associate Director, Mechanical Engineer Collins Aerospace ross.wilcoxon@collins.com

#### ► SUBSCRIPTIONS ARE FREE

Subscribe online at www.electronics-cooling.com

For subscription changes email info@electronics-cooling.com

Reprints are available on a custom basis at reasonable prices in quantities of 500 or more. Please call +1 484-688-0300.

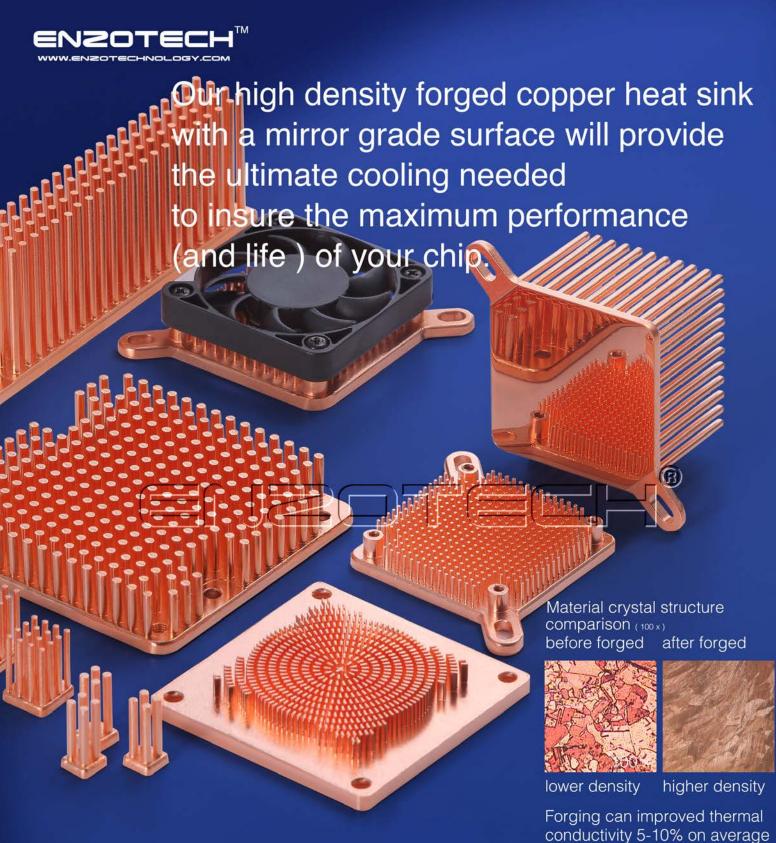

#### ENZOTECHNOLOGY CORP.

Address: 14776 Yorba Ct. Chino, CA 91710 USA

Tel : 909-993-5140 Fax : 909-993-5141

E-mail: info@enzotechnology.com Website: www.enzotechnology.com

www.enzotechnology.com

## **EDITORIAL**

## **Bruce Guenin**Associate Technical Editor

#### In Praise of Thermal Standards

Looking back over the last few decades, we've seen amazing advances in chip functionality as enabled by Moore's law scaling—shrinking CMOS gate size, reduced gate power, increased operating frequencies, and more input/output channels operating at higher bandwidth for data exchange with other devices. These developments, at the chip level, have enabled proportional increases in the performance of individual servers, which, in turn, have propagated to the data center level.

This accomplishment is noteworthy in its own right. It becomes even more so when one figures that the technical developments that made these advances possible involved thousands of different companies, each operating within its own technical niche, but with their collective efforts having enough coherence that the entire enterprise can function amazingly well.

What contributes to this coherence even between competing companies? Many of the company-to-company interactions are confidential, involving the exchange of proprietary information. However, the industry long ago decided that it was to the mutual benefit of competitors in a particular sector of the industry to cooperate through the development and promotion of numerous industry standards of every type imaginable, including, of course, thermal standards.

In this issue, we are pleased to have two articles, each providing an update from the one of the chairmen of the two leading thermal standards organizations, that have played an important role in promoting the development and application of best practices in thermal engineering and disseminating them throughout our industry. These committees are: the JEDEC JC-15 Thermal Standards Committee, chaired by Dr. Jesse Galloway, dealing with chip- and package-level standards; and the ASHRAE Technical Committee 9.9, Chaired by Dr. Dustin Demetriou, developing standards at the server and data center level.

We owe a debt of gratitude to both of these committees, since they face many challenges in fulfilling their respective missions. They must ensure that the scope of their body of standards continually expands to keep up with the constant steam of technical developments in the industry. Even after that is done, they still have to document the standards in a manner that makes them understandable to a diverse, world-wide community of engineers, representing many different levels of expertise.

The above efforts on the part of committee chairmen and members must appear to be rather daunting to much of our readership. However, I can assure you, on the basis of my own experience as a past Chairman of the JC-15 committee, that the rewards of participation are also great. There is abundant satisfaction in seeing a standard that one has contributed to, released to the industry, and having an impact on engineering as it is practiced in the real world. It also represents a great learning experience as committee members collectively explore the trade-offs inherent in the implementation of different technical strategies. The level of detail and nuance in these discussions can often be quite extraordinary. Also, these discussions are often accompanied by a sense of urgency as the participants realize that higher quality standards ultimately benefit the end users and make their jobs easier.

I encourage all of our readers to consider joining a standards committee that best suits their expertise. I'm sure that Drs. Galloway and Demetriou would enjoy learning of your interest.

- Bruce Guenin

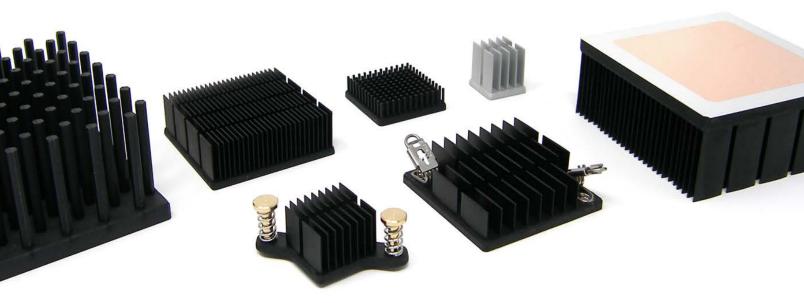

# Alpha's Extensive Products and Services

Tabbed Push Pin

Push Pin

Shoulder Screw

QuickSet

DC-DC Converter

Optical Transceiver

CPU

LED

Push Pin

Shoulder Screw

Spring

Z-Clip

QSZ Clip

Adhesive Tape

Thermal Interface

Fan

#### Same Day Shipping

Over 10,000 items with same day shipping. Heatsinks, attachment hardware and accessories.

#### **Various Attachment Options**

Quickset & QSZ anchor pins require Min. PCB area.

## Online Custom Design

Custom heatsinks can be designed online. No MOQ or tooling fees. Lead time is 1-2 weeks.

#### **Copper Embedded Heatsinks**

Replacement of heat pipe/vapor chamber.

ALPHA Co., Ltd. Head Office www.micforg.co.jp 256-1 Ueda, Numazu City, Japan 410-0316 Tel: +81-55-966-0789 Fax: +81-55-966-9192 Email: alpha@micforg.co.jp ALPHA NOVATECH, INC. USA Subsidiary www.alphanovatech.com

473 Sapena Ct. #12, Santa Clara, CA 95054 USA Tel:+1-408-567-8082 Fax: +1-408-567-8053 Email: sales@alphanovatech.com

# **COOLING EVENTS**

News of Upcoming 2019 & 2020 Thermal Management Events

## 12TH FKFS-CONFERENCE: 'PROGRESS IN VEHICLE AERODYNAMICS AND THERMAL MANAGEMENT'

Haus der Wirtschaft, Willi-Bleicher-Straße 19, 70174 Stuttgart, DE

The FKFS-Conference is an ideal location to get latest information about new car developments, new or improved testing techniques and new or improved calculation procedures. It is an ideal forum to meet leading experts from industry, universities, and other institutions, to exchange ideas and discuss new ones. Furthermore, demonstrations will show state-of-the-art measurement technology applied live in FKFS Wind Tunnels and Laboratories.

► http://fkfs-veranstaltungen.de/index.php?id=143

#### **MWC LOS ANGELES 2019**

Los Angeles Convention Center, Los Angeles, California, USA

Welcome to the era of Intelligent Connectivity—where speed, convenience, and intelligence converge; inspiring new technologies that keep us connected to everything and everyone, while delivering highly contextualized and personalized experiences, when and where you want them.

5G deployments in North America are empowering advances in IoT, AI, Immersive Content, and Disruptive Innovation. MWC Los Angeles 2019 will bring tech industry influencers together to explore this transformation and discover how they can harness it to impact their success.

Join us, October 22-24, 2019 to explore how Intelligent Connectivity will shape the future of our industry, our businesses, and our world.

www.mwclosangeles.com

#### THERMAL LIVE™ 2019

Online Event

Thermal Live<sup>TM</sup> is the electronics and mechanical engineer's free, online resource for education and networking in thermal management. Learn the latest techniques and topics directly from thermal management thought leaders without leaving your seat. Join us for two full days of interactive webinars, product demonstrations, whitepapers, and more. Produced by Electronics Cooling® magazine.

Available now On Demand: All Thermal Live<sup>TM</sup> 2018 Presentations!

▶ www.thermal.live

#### **SEMI-THERM® THERMAL TECHNOLOGIES WORKSHOP 2019**

Microsoft Redmond Campus, Redmond, Washington, USA

In 2019, the workshop is being held at the Microsoft Corporation Conference Center on the Microsoft headquarters campus, near Seattle WA. This new venue allows us to expand the number of attendees and number of technical exhibits.

Speakers and attendees are asked to attend the entire Workshop to encourage greater interaction between registered attendees. Every year, authors and attendees find this Workshop format to be an effective forum for networking between all participants.

www.semi-therm.org

## SEMI-THERM® 36: THE 36<sup>TH</sup> ANNUAL THERMAL MEASUREMENT, MODELING AND MANAGEMENT SYMPOSIUM

Doubletree by Hilton, San Jose, California, USA

See pages 42 – 43 for Semi-Therm's 2020 Technical Program. For program details, registration, exhibition and hotel information, please visit:

www.semi-therm.org

**ONLINE EVENT**

# Ethermally E OCTOBER 22 — 23, 2019

PRESENTED BY ELECTRONICS COOLING®

# WELCOME TO THERMAL LIVETM 2019

## The Largest Single Thermal Management Event of The Year - Anywhere.

Thermal LIVE™ is the electronics and mechanical engineer's free, online resource for education and networking in thermal management. Learn the latest techniques and topics directly from thermal management thought leaders without leaving your seat.

Join us for one full day of interactive webinars, product demonstrations, roundtables, whitepapers, and more.

Produced By:

**COOLING**

## THERMAL LIVE™ 2019 TECHNICAL PROGRAM

OCTOBER 22 - 23, 2019

#### TUESDAY | OCTOBER 22, 2019

BRUCE GUENIN, Ph.D. | 9:00 am ET Associate Technical Editor, Electronics Cooling®

Keynote: Whatever Happened to the Predicted Data Center Energy Consumption Apocalypse? In the early years of the internet between 2000 and 2008, the total energy consumed by data centers in the US increased by 15% per year, representing a doubling of energy consumption in six years and a tripling in nine years. This created a sense of urgency leading to very pessimistic projections about future energy consumption by data centers that persist even to today. The reality is actually quite different, with data center energy consumption increasing at a modest rate of less than 2% per year since 2008. This presentation examines the effect of Moore's Law scaling in improving the inherent energy efficiency of computer, storage, and networking hardware. It also explores the structural changes in the IT industry in which high-end and hyperscale data centers, with state-of-the-art energy-efficient technologies, produce an increasing fraction of the total IT workload in the US.

TIM JENSEN | 10:15 am ET Senior Product Manager for Engineered Solder Materials, Indium Corporation

#### Liquid Metal Thermal Interface Material Innovations for High-Performance Devices

The idea of using liquid metals as a thermal interface material (TIM) is not new. Liquid metal provides very high thermal conductivity, as well as low interfacial resistance when in contact with most surfaces; however, there have always been a number of material and process challenges that limited their adoption. This presentation with review those challenges while discussing liquid metal material innovations that enable higher performance as compared to conventional TIMs.

NICOLAS MONNIER | 11:15 am ET

Product & Marketing Specialist, Stäubli North America

Product Demo: Design Consideration for the Mechanical Integration of Quick Disconnects in **Liquid Cooled Electronic Systems**

Liquid cooling for heat dissipation in electronic systems is becoming a requirement as the power of components is increasing, as well as density. The use of performant quick disconnects allowing the hot swap of the active components from the static structure is understood and embraced by the thermal community. As theory becomes practice, it becomes the responsibility of the mechanical engineer to integrate that component reliably. The presentation will go over some of the mechanical and practical solutions proposed to interface with the system architecture. These must be considered at the early stage of the global design. Their proper integration will influence the reliability of the liquid line as well as the total cost of the system.

#### TUESDAY | OCTOBER 22, 2019 | CONTINUED

DANNY LEONG | 12:00 pm ET

Principal Application Engineer, Technical Customer Service, Henkel

#### Raising Reliability of Devices for 5G Telecom Infrastructure

The coming era of 5G mobile communications has users excited about the possibilities and broadband systems designers and manufacturers a bit nervous about the realities. While handheld devices may have the required chipsets, infrastructures must be able to manage the huge amounts of data and speeds required to satisfy 5G demands. Reliable 5G networks will clearly require a host of solutions – at the printed circuit board level all the way up to the final system enclosure – to deliver on the huge expectations. Keeping all systems go also means keeping all systems cool, making thermal management one of the most critical pieces of the 5G solution. Henkel's has recently launched BERGQUIST® GAP PAD® ultra-low modulus portfolio especially in this 5G telecom infrastructure application.

CHRISTIAN MIRAGLIA | 1:15 pm ET

Applications Engineering Manager, Fujipoly

#### Understanding Thermal Gap Filler Pads, PCB Deflection and Stress

Managing compression force and stress is critical in any application that incorporates gap filler pads as a thermal interface. In this webinar we will look at the compression characteristics of thermal gap filler pads. We will apply this understanding to a PCB assembly. Webinar attendees will have a better understanding of what basic analytical techniques and tests can be performed to understand stress as well as defection in both gap filler pads and PCB.

#### WEDNESDAY | OCTOBER 23, 2019

JEFF PETERS | 12:00 pm ET

Project Manager, Thermal Management, CPC (Colder Products Company)

#### The Future is Now: Advanced Connector Solutions for Liquid Cooling

CPC, a global leader in QDs for liquid cooling applications, will cover key thermal engineering factors to consider in specifying QDs in liquid cooling systems. Jeff Peters, mechanical engineer and CPC thermal management product manager, will describe the evolution and characteristics of various connector options for a range of applications as well as provide comprehensive information about the future of QDs—engineered polymers. Just coming to market, advanced thermoplastic QDs are lighter-weight alternatives to stainless steel and meet or exceed requirements for thermal performance, chemical compatibility, anti-corrosion and condensation management, and long-term, leak-free operation.

## THERMAL LIVE™ 2019 TECHNICAL PROGRAM

OCTOBER 22 - 23, 2019

#### **WEDNESDAY | OCTOBER 23, 2019 | CONTINUED**

KIMBERLY FIKSE | SPEAKER | 1:15 pm ET Applications Engineer, ACT (Advanced Cooling Technologies)

**ANDY SLIPPEY** | Q & A MODERATOR

Product Development Engineer, II ACT (Advanced Cooling Technologies)

#### Passive and Active Two-Phase Cooling for Power Electronics

Advanced Cooling Technologies will review strategies for managing the rising waste heats from Mosfets, IGBTs and other Power Electronics modules using two-phase technology. This session will focus on loop thermosyphon and pumped two-phase (P2P) solutions. Both technologies provide high thermal capacity, while also provide unique benefits to power electronics, such as dielectric working fluids and packaging flexibility. Please join us to review theory and practical applications for these emerging technologies.

BRANDON NOSKA | 3:00 pm ET Sheetak

#### Advancements in Solid-State Cooling Technologies

This presentation will cover market trends driving the need for increased efficiency and miniaturization of solid-state cooling technologies. We will show different device architectures to achieve higher temperature differentials with increased COP. In addition, we will describe a novel thin film cooling technology platform to enable more efficient, higher performance micro coolers for a broad spectrum of optoelectronics and other electronics applications.

ANANTH SRIDHAR | 4:15 pm ET Applications Engineer, OnScale

#### Next-Generation Electronics Packaging Design with OnScale Cloud Engineering Simulation

In this presentation, we describe how OnScale supports efficient solutions to highly complex design issues in Electronics Packaging with its highly parallelized proprietary multiphysics solvers on the Cloud. Further, we demonstrate how OnScale's revolutionary platform lends itself for multi-objective multi-variable optimizations studies of advanced package designs including 1000s of models that can be run at a fraction of time and cost compared to legacy simulation software.

### THERMAL LIVE™ 2019 SPONSORS

AAVID, THERMAL DIVISION OF BOYD CORPORATION **ACT (ADVANCED COOLING TECHNOLOGIES) CPC (COLDER PRODUCTS COMPANY)**

**FUJIPOLY**

HENKEL

INDIUM CORPORATION

**ONSCALE**

**SHEETAK**

STÄUBLI NORTH AMERICA

## INTERESTED IN ATTENDING THERMAL LIVE™ 2019? REGISTER TODAY FOR FREE AT

## WWW.THERMAL.LIVE

#### INTERESTED IN PRESENTING AT THERMAL LIVE™?

#### For Marketing Opportunities, Contact Our Business Development Team:

#### **GRAHAM KILSHAW**

e: Graham@lectrixgroup.com p: 610.382.5885

#### IAN QUINN

e: lan@lectrixgroup.com p: 610.382.5888

#### JAN WARD

e: Jan@lectrixgroup.com p: 610.382.5891

#### MARK PANTALONE

e: Mark@lectrixgroup.com p: 267.225.7333

### **CALL FOR PAPERS**

36th Annual Semiconductor Thermal Measurement, Modeling and Management Symposium March 16-20, 2020 at the DoubleTree by Hilton, San Jose, CA USA

#### **About SEMI-THERM**

SEMI-THERM is an international symposium dedicated to the thermal management and characterization of electronic components and systems. Its goals are to:

- Provide knowledge covering all thermal length scales from integrated circuits to facility levels

- Foster discussions between thermal engineers, professionals and industry experts

- Encourage the exchange of information on academic and industrial advances in electronics cooling

**Topics Include:** Component/Board/System Thermal Design, Fluid Movers, Acoustics, Advanced Materials, Measurement Methods, Modeling & Simulation, Additive Manufacturing, Reliability, etc.

**Applications Include:** Processors/ICs/Memory, 3-D packaging, Computing Systems, Data Centers, Portable/Consumer/Wearable Electronics, Power Electronics, Harsh Environments, Defense/Aerospace Systems; Solid-State Lighting & Cooling, Biomedical; Micro/Nano-scale Devices, etc.

#### **Symposium Highlights**

Technical Sessions

Technical Short Courses

Tutorials

Vendor Exhibits Vendor Workshops Product Tear Downs Panel Discussions

Poster/Dialog Session

#### Three options for participating in the technical program:

**Peer-reviewed paper:** Submit a full <u>manuscript</u> for peer review in October. Authors notified of acceptance in November. Reviewer comments provided to authors in December. Final manuscript due in January. Manuscripts will be provided to conference attendees.

**Non-peer-reviewed paper:** Submit an <u>extended abstract</u> (2-5 pages) that describes the scope, contents, key results, findings and conclusions. Authors notified of acceptance in November. Final manuscript due in January. Manuscripts will be provided to conference attendees.

**Presentation only:** Submit an <u>extended abstract</u> (2 -5 pages) that describes the scope, contents, key results, findings and conclusions. Authors notified of acceptance in November. Final presentation slides are due in March. Presentations will be provided to conference attendees.

**Awards:** All papers with manuscripts are eligible for the Best Paper Award. Student papers presented at the conference are eligible for Student Scholarships. Presentation-only submissions are not eligible for awards.

| Manuscripts and extended abstracts submission deadline | Date that authors are notified of acceptance | Photo-ready full manuscript submission due date |

|--------------------------------------------------------|----------------------------------------------|-------------------------------------------------|

| Oct 4, 2019                                            | Nov 15, 2019                                 | Jan 17, 2020                                    |

## **Larger Errors with Smaller Stuff**

**Ross Wilcoxon**

Associate Technical Editor

ong time readers of Electronics Cooling® will undoubtedly recall one of our former editors: Clemens Lasance. One of Clemens' many contributions to the magazine was the creation of the original "Thermal Facts and Fairy Tales" column, which provided a forum for him to discuss a variety of issues related to the use and misuse of information related to the topic of electronics cooling and thermal management. I have known Clemens for many years, and I feel confident that when I describe him as "willing to say what he thinks," it is unlikely to provoke an argument from other people who know him. One topic that Clemens has always been willing to express an opinion on is the use of empirical correlations in engineering analysis.

In a number of Electronics Cooling® articles, Clemens outlined his many concerns regarding the use of empirical correlations. One of these concerns included the fact that, even with the simple geometry of a flat plate with natural convection, correlations developed by different researchers for the same geometry can vary by 100% [1]. He was also pointed out that the incorrect use of non-dimensional parameters can lead to correlations that do not exist. For example, if a given configuration is tested with a wide range of the critical length scale (such as diameter), the Nusselt number will increase with Reynolds number even if the convection coefficient is constant [2]. Another concern was with the use of correlations developed for simple geometries, such as flow channels, for estimating the performance of more complex systems such as flat plate heat sinks. The pressure drop of a heat sink estimated using different correlation approaches was as much as twice the value determined with experiments [3]. The general conclusions from [1-3] can be summarized as "geometrically and physically complex phenomena cannot be described by simple equations" [2].

An additional concern with using correlations is the fact that they are typically only valid over a specific range of conditions, such as Reynolds number, length scales, etc. Even if one is a fervent believer that empirical correlations are accurate, it is still critical that one understands the conditions under which a correlation was developed, and ensures that the correlation is considered to be appropriate for the specific case in which it is being used.

While Clemens' concerns with correlations are certainly valid, I didn't always take them as seriously as I possibly should have. I felt that most the more widely accepted correlations were probably reasonably accurate and most engineers are aware enough to be sure that a given correlation is appropriate for their application. I was recently reminded that this isn't always the case when I came across a paper that dealt with from a near-nanoscale structure. The paper used a fairly widely known correlation [4] to estimate the free convection from a very small cylinder that had a diameter of a few microns. The results reported in the paper had what seemed to be quite high heat transfer rates, given that it was for a case of natural convection. Upon further review of the details of the analysis, it turned out that the conditions under which the analysis was done were below the range for which the correlation was considered to be appropriate. The very small diameter led to an extremely small Rayleigh number that was at least two orders of magnitude below the data from which the correlation was developed. This led to a heat transfer, in free convection, that was more than 5,000 W/m2 K.

A close review of reference [4] reveals a few interesting details. First, the log-log charts that compile dimensionless data appear to have errors in the labels for the y-axis. While the correlation appears to be correct despite the errors in the plots, this is a reminder that empirical correlations should be verified to ensure that an error did not find its way into the analysis. Another issue of note in the original paper is an explicit recognition that the correlation is not valid for Rayleigh numbers (Ra) less than 10<sup>-6</sup>, which is much larger than the situation calculated for a micron-scale cylinder. Using empirical correlations can always be somewhat dangerous—particularly when they are used outside the range of conditions for which they were developed.

When I first began writing this article, I was fairly certain that I was writing about an excellent example of an empirical correlation being badly misused. The micron-scale cylinder in the paper that I found had a Ra on the order of 10<sup>-10</sup>, which was four orders of magnitude outside the appropriate range for the correlation. However, after spending far more time trying to interpret reference [5] than I ever intended (primarily because of the errors in the scales used in the plots), it appears that there are data for ex-

tremely small Ra values and the error in using the correlation for the micron-scale may closer to a factor of 2, rather than the orders of magnitude that I first thought.

While the concerns about correlations discussed in references [1-3] are certainly valid, I still believe that empirical correlations can be useful for generating preliminary assessments of a system, as long as their limitations are recognized, and the application is sufficiently similar to the test conditions that were used to generate the correlation. This becomes more important, and challenging, as we move into applications with world of micro- and nano-scale geometries. These tiny geometries can lead us astray by introducing errors because we are extrapolating them to conditions that are not relevant. Or, they can possibly lead us to significant heat transfer improvements (5 kW/m² K in free convection!) if they are still correct at those geometries and we can determine ways to exploit them.

#### **REFERENCES**

- [1] https://www.electronics-cooling.com/2010/04/thermal-facts-and-fairy-tales-most-of-us-live-neither-in-wind-tunnels-nor-in-the-world-of-nusselt/ (accessed 8/4/19)

- [2] https://www.electronics-cooling.com/2011/09/thermal-facts-and-fairytales-does-your-correlation-have-an-imposed-slope/ (accessed 8/4/19)

- [3] https://www.electronics-cooling.com/2013/12/heat-sink-correlations-design/ (accessed 8/4/19)

- [4] S. W. Churchill and H.S Chu, "Correlating Equations for Laminar and Turbulent Free Convection from a Horizontal Cylinder", Int. J. Heat Mass Transfer, Vol 18, pp. 1049-1053, 1975.

# Thermal Interactions Between High-Power Packages and Heat Sinks, Part 2

Reprinted from the March, 2011 issue. To be followed by a new Part 3, planned for Spring, 2020 issue.

**Bruce Guenin**

Associate Technical Editor

#### **INTRODUCTION**

hese days, many thermal engineers face the challenge of defining effective heat sink cooling solutions for high power processors and ASICs (Application-Specific Integrated Circuits). The usual practice would be to calculate a value of JA (junction-to-air thermal resistance) for the combined package/heat sink assembly and compare it to the requirements of the application.

Traditionally, in performing this sort of calculation, one would first obtain a value of  $\Theta_{\rm IC}$  (junction-to-case thermal resistance) from the packaging supplier and a value of  $\Theta_{\rm SA}$  (sink-to-air thermal resistance) from the heat sink supplier. Since the heat sink test is usually performed with a uniform heat flux applied over the entire base, one would need to correct the value of  $\Theta_{\rm SA}$ , assuming that the heat is transferred into the heat sink uniformly over the entire contact area between the package and the heat sink. A very accurate and efficient method of doing this has been described in this publication [1]. One would then make assumptions about the thickness and thermal conductivity of prospective thermal interface materials (TIMs) to provide effective thermal contact between the package and the heat sink. The thermal resistance of this particular TIM, between the package case and the heat sink base (namely, TIM2) is referred to as  $\Theta_{\rm CS}$ .

The three thermal resistance values would then be added up to obtain the desired value of  $\Theta_{IA}$  per the following expression:

$$\Theta_{JA} = \Theta_{JC} + \Theta_{CS} + \Theta_{SA} \tag{1}$$

This procedure worked well enough when power levels were lower than today. The accompanying higher values of thermal resistance masked the presence of certain thermal interactions that are important sources of error for high-power/low-thermal-resistance components. The fact that these resistances are not boundary-condition independent means that their precise value depends upon the details of the heat transfer between the various components [2]. This is due to the fact that these thermal resistance metrics are the product of a methodology, which ultimately represents a measurement approach: namely the temperatures T<sub>p</sub>, T<sub>C</sub>, and T<sub>S</sub>, all are determined at the geometric center of each component [3].

Such single-point temperature measurements do not provide direct information regarding the heat flux distribution that could be useful in defining a more robust thermal resistance metric.

#### **SUMMARY OF PART 1**

Part 1 of this article was devoted to exploring the nuances of the interactions between these components, particularly as to their effect on the heat flux distribution in the path between the package case and the heat sink base [4].

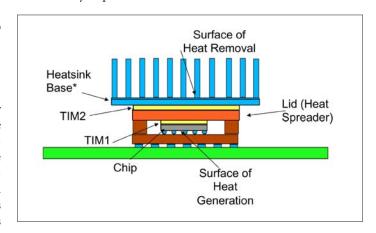

Figure 1 depicts a typical configuration of a flip-chip cavity package containing a copper lid in contact with the base of a heat sink. Those components depicted using bold colors are explicitly represented in the Finite Element Analysis (FEA) model. These constitute the primary heat flow path, from the chip to the heat sink. Those drawn with the faint colors are present in the physical assembly, but are not explicitly represented in the model. These include the heat sink fins and the package substrate and the printed circuit board (PCB) to which the package is electrically interconnected. The cooling effect of the fins is accounted for by the use of an effective heat transfer coefficient ( $h_{\rm EFF}$ ) applied to the top of the heat sink base. The heat flow through the package substrate to the PCB is simply ignored, since in a high-power package, it is of secondary importance.

Figure 1. Diagram of high-power package attached to a heatsink. Components in bold color are explicitly represented in the model. Those in a faint color are part of the physical assembly, but are not represented in the model.

| Model Dimensions, Materials, and Properties |                |           |             |                    |          |                      |  |  |  |

|---------------------------------------------|----------------|-----------|-------------|--------------------|----------|----------------------|--|--|--|

| Layer No.                                   | Component      | Thickness | Width       | Material           | Th. Cond | Heat Transfer Coef.  |  |  |  |

|                                             |                | (mm)      | (mm)        |                    | (W/mK)   | (W/m <sup>2</sup> K) |  |  |  |

| 1                                           | Die            | 0.5       | 13          | Si                 | 111      | N/A                  |  |  |  |

| 2                                           | TIM1           | 0.1       | 40          | Ag-Epoxy           | 2        | N/A                  |  |  |  |

| 3                                           | Lid            | 0.5       | 40          | Cu                 | 390      | N/A                  |  |  |  |

| 4                                           | TIM2           | 0.05      | 40          | Grease             | 1        | N/A                  |  |  |  |

|                                             |                | 2         | 40, 70, 100 | Low-Cond Al Alloy  | 166      | 50, 200, 1000, 2000  |  |  |  |

| 5 H                                         | Heat Sink Base | 2         | 40, 70, 100 | High-Cond Al Alloy | 240      | 50, 200, 1000, 2000  |  |  |  |

|                                             |                | 6         | 40, 70, 100 | Cu                 | 390      | 50, 200, 1000, 2000  |  |  |  |

Table 1. Model Dimensions, Materials, and Properties.

*Table I* defines the package construction and the variations in the heat sink design explored. The heat sink designs and the large spread in  $h_{\text{EFF}}$  represent a wide range of thermal performance.

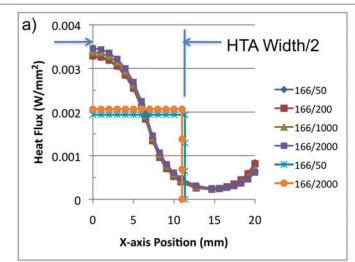

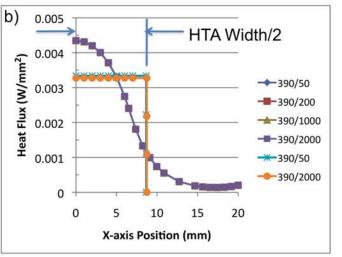

The curved data sets in *Figure 2* demonstrate the heat flux distribution through the TIM2 material determined for the lowest and highest conductivity heat sinks, at a value of heat sink width,  $w_{HS} = 70$  mm, and over the full range of  $h_{EFF}$ . They show that, even for a package with a 1 mm thick lid made of pure copper, the heat flux is concentrated in the center of the package, in stark contrast to the traditional assumption of uniform heat flow over the package area.

The rectilinear data sets represent a uniform flux distributed over a specified area defined herein as the Heat Transfer Area (HTA). The HTA was defined in Part1 as: the area bounding a uniform flux region which produces the same value of  $\Theta_{\rm SA}$  as the FEA simulation with non-uniform flux distribution, each with the same total power. This procedure was decided upon because of its sim-

plicity, rather than pursuing the more involved process of analyzing the actual flux distributions. For a square shaped die and package, such as in the current example, it is convenient to refer to the HTA Width, which provides a more intuitive sense of the size of the area than referring to the area itself.

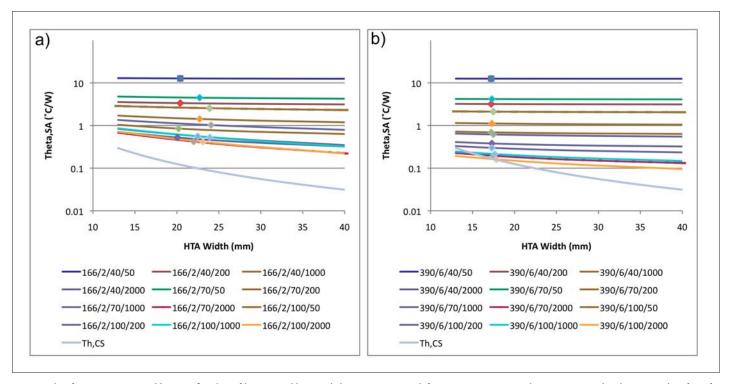

#### DERIVATION AND USE OF THE HTA CONCEPT

Figure 3 (see page 22) shows curves of  $\Theta_{SA}$  versus the full range of values of HTA Width possible with the present package: from the die width (13 mm) to the full package width (40 mm). These curves were calculated using FEA with only the heat sink base in the solid model and applying the flux at HTA values equal to 13, 20, 30, and 40 mm sq. (Note that this calculation could have been performed with equal accuracy using the method in *Reference 1*.) The curves were created using a third-order linear regression technique.

The symbol overlapping each curved line represents a value of HTA which yields a value of  $\Theta_{SA}$  equal to that calculated in the

Figure 2. Plot of heat flux in TIM2 region, at specific values of k<sub>HS</sub> and h<sub>EFF</sub>. w<sub>HS</sub> is constant at 70 mm. Curved data set: values extracted from full FEA model. Rectilinear data set: representation of HTA with constant flux. a) low conductivity Al heat sink; b) Cu heat sink.

Figure 3. Plot of  $\Theta_{SA}$  versus HTA Width at specific values of  $k_{HS'}$  w<sub>HS'</sub>, and  $h_{EFF}$ . Symbols represent FEA result for  $\Theta_{SA}$  at intersection with  $\Theta_{SA}$  curves, used to determine value of HTA for each heat sink condition. Lowest curve is  $\Theta_{CS}$  vs HTA. a) low conductivity Al heat sink; b) Cu heat sink.

full FEA model of the package in contact with the heat sink. A spreadsheet solver was used in the calculation. For the low conductivity heat sink they are clustered in the range of HTA Widths between 20 and 24 mm. For the high conductivity heat sink they are in the narrower range between 17 and 18 mm.

It is reasonable to expect that the HTA concept should be useful in the calculation of  $_{CS}$ , as suggested by a comparison of the uniform flux distribution over the HTA and the actual flux distribution in Figure 2. Since the flux is assumed to be uniform within the HTA, the following expression, representing one-dimensional heat flow, can be used to calculate  $\Theta_{CS}$ :

$$\Theta_{CS} = \frac{t_{TIM 2}}{k_{TIM 2} * HTA} \tag{2}$$

Where  $t_{TIM2}$  and  $k_{TIM2}$  are the thickness and thermal conductivity of TIM2, respectively.  $\Theta_{CS}$  is plotted as a function of HTA in *Figures 3a* and *3b*. It is useful to compare the magnitude of  $\Theta_{CS}$  and  $\Theta_{SA}$  for the two heat sinks studied. For the low conductivity heat sink,  $\Theta_{CS}$  is much lower than the lowest value of  $\Theta_{SA}$ . In the case of the high conductivity heat sink,  $\Theta_{CS}$  is comparable in magnitude to the lowest values of  $\Theta_{SA}$ . This fact will be relevant during the error analysis.

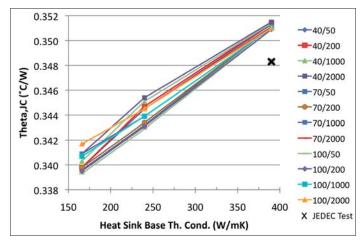

Figure 4 shows the calculated values of  $\Theta_{JC}$ , plotted versus the heat sink thermal conductivity,  $k_{HS}$ , for all the cases studied. It also displays a value of  $\Theta_{JC}$ , calculated under simulated JEDEC-standard conditions (water-cooled cold plate, 2-mm-thick copper top plate) [5]. Note this it is a bit lower in magnitude (0.002°C/W) than the

values of  $\Theta_{JC}$  calculated for the package in contact with the copper heat sink, due to its greater thickness (6 mm vs. 2 mm).  $\Theta_{JC}$  values calculated for the lowest conductivity heat sink are about 0.01°C/W less than the simulated test value. Comparing these differences with the values of  $\Theta_{SA}$  and  $\Theta_{CS}$  in *Figure 3* suggest that these deviations in  $\Theta_{JC}$  in the full model from the simulated test value will not be a significant source of error.

Figure 4. Plot of  $\Theta_{\rm IC}$  versus vs  $k_{\rm HS}$  at specific values of  $w_{\rm HS}$  and  $h_{\rm EFF}$ : extracted from full package/heat sink FEA simulation. Black X symbol represents simulated JEDEC test result.

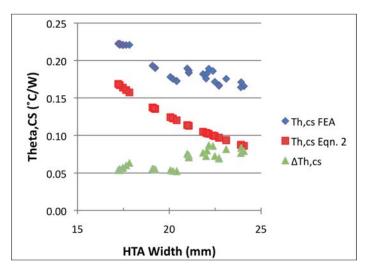

Figure 5 (see page 23) contains a plot of  $\Theta_{\rm CS}$  versus HTA Width. The values of  $_{\rm CS}$  were calculated using one of two methods: 1) extraction from the full package/heat sink FEA simulation and 2)

calculation using *Equation 2* and the values of HTA calculated using the method illustrated in *Figure 3*. The HTA-calculated values are approximately 0.08 °C/W less than the FEA-calculated values for the low conductivity heat sinks and 0.05 °C/W less for the high conductivity heat sinks. Comparing these discrepancies with the values of  $\Theta_{\rm SA}$  in *Figure 3*, suggest that this will be a more significant source of error.

Figure 5. Plot of  $\Theta_{\rm CS}$  versus HTA. Blue symbols: values extracted from full package/heat sink FEA simulation. Red symbols: values calculated from Equation 2.

## SIMPLIFIED THETA, JA CALCULATIONS USING THE HTA CONCEPT

It is hoped that the preceding analysis has made it clear that the assumed size of the area bounding the heat flow between the package and the heat sink has a significant influence on the resultant values of  $\Theta_{CS}$  and  $\Theta_{SA}$  and, consequently,  $\Theta_{JA}$ . This section will explore the accuracy of analytic calculations making various assumptions regarding the size of this bounding area.

| <b>Analytical Model Assumptions and Error Analysis</b> |                          |       |     |      |  |  |  |  |

|--------------------------------------------------------|--------------------------|-------|-----|------|--|--|--|--|

| Method #                                               | Areas                    | Error |     |      |  |  |  |  |

| Method #                                               | Assumed in               | Avg   | Max | Min  |  |  |  |  |

| 1                                                      | Pkg                      | -21%  | -2% | -36% |  |  |  |  |

| 2                                                      | Avg HTA, all<br>cases    | -5%   | 3%  | -16% |  |  |  |  |

| 3                                                      | HTA - Avg per<br>HS Type | -4%   | -1% | -10% |  |  |  |  |

| 4                                                      | Specific HTA value       | -4%   | 0%  | -9%  |  |  |  |  |

Table 2. Analytical Model Assumptions and Error Analysis.

Table 2 describes four methods, which differ in this assumption.

- Method #1 assumes the bounding area = the package area.

- Method #2 assumes the bounding area = a single value of HTA averaged over all the cases studies.

- Method #3 assumes the bounding area = average of HTA calculated for each of three heat sink configurations.

- Method #4 assumes the bounding area = the specific value of HTA calculated individually for each case.

$\Theta_{IA}$  is calculated using *Equation 3*:

$$\Theta_{JA} = \Theta_{JC,TEST} + \Theta_{CS}(Area)[Eqn.2] + \Theta_{SA}(Area)[Ref.1]$$

(3)

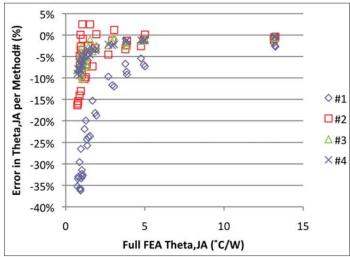

The results calculated using each method were compared to the  $\Theta_{JA}$  values calculated using the original FEA model. A complete listing of all the  $\Theta_{JA}$  results is provided in *Table 2* of Part 1 of this article [4]. The results are shown in *Figure 6*. The error is summarized in *Table 2*.

Figure 6. Error in value of  $\Theta_{JA'}$  calculated using Equation. 3 versus  $\Theta_{JA'}$  extracted from full package/heat sink FEA simulation. Results reflect effect of four different assumptions regarding the method of calculating the heat transfer area.

All the methods show an increase in the absolute error as the value of  $\Theta_{\rm JA}$  gets smaller. Method #1, using the package size for the heat transfer area, has an error of less than 10% for values of  $\Theta_{\rm JA}$  of 3°C/W and greater. For  $\Theta_{\rm JA}$  values of less than this, the error grows to 36%. Using the average HTA value of 20.6 mm, in Method #2 leads to a large reduction of error, with the maximum error equal to 16%. Further improvement is obtained with Method #3, using the value of HTA averaged for each heat sink design. Here the maximum error is 10%. Method #4, with a separate value of HTA applied to each case represented a small improvement with the maximum error equal to 9%. As indicated earlier, most of the error in Methods #4 and 5 is due to the  $\Theta_{\rm CS}$  term.

#### **CONCLUSIONS**

The past practice of assuming a uniform heat flow between a package and heat sink over the full area of the package is shown to be inadequate with high-power packages. The HTA method uses the same assumption of a uniform flux as before, but uses a value for the bounding area determined from a detailed finite element analysis of the package and heat sink. For this method to become more widely useful, correlations are needed to generate appropriate HTA values for arbitrary package and heat sink designs. Once the appropriate HTA is on hand, then the remainder of the calculation is straightforward.

#### **REFERENCES**

- [1] Lee, S., "Calculating Spreading Resistance in Heat Sinks," ElectronicsCooling, Vol. 4., No. 1, January, 1998.

- [2] Lasance, C, "Heat Spreading: Not a Trivial Problem," ElectronicsCooling, Vol. 14, No. 2, May, 2008.

- [3] JEDEC Standard, JESD51-12, "Guidelines for Reporting and Using Electronic Package Thermal Information." Available for free download at www.jedec.com.

- [4] Guenin, B, "Thermal interactions Between High-Power Packages and Heat Sinks, Part 1, ElectronicsCooling, Vol. 16, No. 4, Winter, 2010.

- [5] JEDEC Standard, JESD51-14, "Transient Dual Interface Test Method for the Measurement of the Thermal Resistance Junction to Case of Semiconductor Devices with Heat Flow Through a Single Path." Available for free download at www.jedec.com.

## **Summary of the IEEE ITherm 2019 Conference**

John F. Maddox, Ph.D., P.E.

Assistant Professor of Mechanical Engineering, University of Kentucky john.maddox@uky.edu

he IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm) was held at the Cosmopolitan Hotel and Casino in Las Vegas, NV from May 28-31, 2019. This was the 31st Anniversary of ITherm, first held in 1988. The conference was historically held every other year until 2016 when it switched to an annual schedule, making this the 18th ITherm. ITherm 2019 was sponsored by the IEEE Electronics Packaging Society (EPS) and co-located with the 69th Electronic Components and Technology Conference (ECTC 2019).

The ITherm 2019 program consisted of 18 professional development workshops on Tuesday, May 28, 2019, followed by three full days of technical presentations in four tracks with 50 sessions, in which 181 papers were presented. Additional technical events included three keynote addresses, five panels, five technology talks, a student poster competition, and an Art-in-Science competition. Of note was a presentation session by students competing in the second annual heat sink design competition, hosted by ASME/ K16 and EPS. There were also two panels held jointly with ECTCthe ECTC/ITherm Young Professionals Panel and the ECTC/ITherm Joint Women's Panel, "Unleashing the Power of Diversity in the Workforce." Both panels were sponsored by EPS and provided an opportunity for closer interaction between the attendees of the two conferences.

This year saw several new additions to the conference, including an improved mobile app, a heat sink design competition, and demonstrations of air, dry ice, and liquid nitrogen cooling by the Oregon State University Overclocking team. An ITherm LinkedIn page was introduced in 2018, which we invite you to join to keep up with announcements and deadlines for ITherm 2020.

#### RICHARD CHU ITHERM AWARD FOR EXCELLENCE

Prof. John R. Thome was awarded the Richard Chu ITherm Award for Excellence for his pioneering work on multiphase flows. Dr. Thome is Professor-Emeritus of Heat and Mass Transfer at the Ecole Polytechnique Fédérale De Lausanne (EPFL), Switzerland, and founder of JJ Cooling Innovation Sàrl in Laussane. Through decades of research, his work has produced new insights into micro channel flow boiling, new flow visualization/image processing techniques, flow stabilization, heat transfer models, flow pattern maps, micro-two-phase cooling systems, and numerical modeling of bubbly/slug flows.

On the first day of the conference, Dr. Guarang Choksi, vice president of technology development and director of assembly and test technology development at Intel, gave a keynote address entitled "Component Integration vs. Product Differentiation: Electronic Packaging Choices for Heterogeneous Assembly & Test." Dr. Choksi discussed the need for interdisciplinary tools for analysis, simulations, and characterization to meet to heterogeneous packaging needs of the future as we move toward 2.5D and 3D architectures.

On the second day of the conference, Dr. Andrew Alleyne, Ralph & Catherine Fisher Professor, University of Illinois, Urbana-Champaign, gave a keynote address entitled "A Systems Approach to Management of Transient Thermal Systems for Mobile Electrification." Dr. Alleyne illustrated the use of a systems-based framework to control the complex electro-thermal interconnected subsystems on board modern transportation platforms.

On the final day of the conference, Cullen Bash, vice president and director of the Systems Architecture Lab at Hewlett Packard, gave a keynote address entitled "Computing beyond Moore's Law." This talk described the transition from traditional CPU driven computing to a memory and data driven model with specialized devices and the challenges this transition places on traditional architectural elements.

#### BEST AND OUTSTANDING PAPERS

An awards luncheon was held on the final day of the conference, at which awards for the best and outstanding papers in each track, based on judging from reviews and inputs from session and track chairs, were unveiled to the attendees.

#### **Best Papers**

Component Level Thermal Management

• Piyas Chowdhury, Kamal Sikka, Alfred Grill, Dishit P. Parekh, "Optimal Filler Sizes for Thermal Interface Materials," IBM.

System Level Thermal Management

• Shurong Tian, Todd Takken, Mark Shultz, Chris Marroquin, Vic Mahaney, Yuan Yao, Michael J Ellsworth Jr, Anil Yuksel, Paul Coteus, "A Single Flexible Cold Plate Cools Multiple Devices," IBM.

Mechanics and Reliability

• Rainer Dudek, Kerstin Kreyssig, Sven Rzepka, Michael Novak,

Wolfgang Gruebl, Peter Fruehauf, Andreas Weigert, "Comparisons of Solder Joints Fatigue Life Predictions and Several Long-Term Testing Results," Fraunhofer ENAS Micro Materials Center, Continental, and Siemens.

Emerging Technologies & Fundamentals

Ziqi Yu, Zongqing Ren, Jaeho Lee, "Investigation of Thermal Metamaterials Based on Nanoporous Silicon Using Ray Tracing and Finite Element Simulations," University of California — Irvine.

#### **Outstanding Papers**

Component Level Thermal Management

Prabhakar Subrahmanyam, Arun Krishnamoorthy, "Micro-Scale Nozzled Jet Heat Transfer Distributions and Flow Field Entrainment Effects Directly on Die," Intel.

System Level Thermal Management

Anirudh Krishna, Jin Myung Kim, Juyoung Leem, Michael Cai Wang, SungWoo Nam Jaeho Lee, "Dynamic Radiative Thermal Management by Crumpled Graphene," University of California—Irvine and University of Illinois at Urbana Champaign.

Mechanics and Reliability

· A R Nazmus Sakib, Richard S Lai, Sandeep Shantaram, "Ef-

fects of Solder Mask Application Method on the Reliability of an Automotive Flip Chip PBGA Microcontroller," NXP Semiconductors.

Emerging Technologies & Fundamentals (Tie)

- Martinus Arie, David Hymas, Farah Singer, Amir Shooshtari, Michael Ohadi, "Performance Characterization of a Novel Cross-Media Composite Heat Exchanger for Air-to-Liquid Applications," University of Maryland.

- Aaditya Anand Candadai, Justin Weibel, Amy Marconnet, "A Measurement Technique for Thermal Conductivity

Characterization of Ultra-High Molecular Weight Polyethylene Yarns Using High-Resolution Infrared Microscopy,"

Purdue University.

We are also pleased to announce that the ITherm 2019 Proceedings have been forwarded to the IEEE Xplore Digital Library and will be posted soon. Papers appearing in the Table of Contents are available for access and download, along with listings of our Keynote Speakers, Tech Talks, Panels, Sponsors, and Exhibitors.

## **ASHRAE Technical Committee 9.9: Mission Critical** Facilities, Data Centers, Technology Spaces, and **Electronic Equipment**

#### Dustin Demetriou, Ph.D.

Senior Engineer, IBM Corporation dustin\_demetriou@electronics-cooling.com

#### **NOMENCLATURE**

A1, A2, ASHRAE allowable thermal envelopes as defined in Thermal Guidelines for Data Processing A3, A4 Environments that represent where IT manufac-

turers test equipment to ensure functionality

*ASHRAE* American Society of Heating, Refrigerating and

Air-Conditioning Engineers

**CAGR** Compound Annual Growth Rate

**CITEA** SHRAE Compliance for IT Equipment

Datacom Data processing and communication facilities,

> that include rooms or closets used for communication, computers, or electronic equipment

**DCIM** Data Center Infrastructure Management

ELC Electrical Loss Component per ANSI / ASHRAE

> Standard 90.4 - 2016. The design ELC is the combined losses of three segments of the electrical chain: incoming electrical service segment,

UPS segment, and ITE distribution segment.

ESD Electro-static discharge

**HVAC** Heating, ventilation and air conditioning

ITInformation Technology

MLCMechanical load component per ANSI /

ASHRAE Standard 90.4 – 2016 is calculated by the sum of all cooling, fan, pump, and heat rejection annual energy use divided by the data center ITE energy (annualized MLC) or the sum of all cooling, fan, pump, and heat rejection design power divided by the data center

ITE design power (design MLC).

TC**Technical Committee**

W1 - W5ASHRAE liquid cooling classes for liq-

uid-cooled IT equipment

#### HISTORY OF ASHRAE TC 9.9

n 1999, a group of thermal engineers from different IT manufacturing companies formed a thermal management consortium. This consortium evolved into ASHRAE Technical Committee 9.9 (TC 9.9). This history was documented in articles by Roger Schmidt (2012) [1] and Don Beaty (2005) [2]. This article serves as a continuation of those articles in documenting the activities of TC 9.9 since then.

TC 9.9 was formed in response to the lack of effective information transfer between the building, HVAC, and IT industries. Its mission is to be recognized by all areas of the datacom industry as the unbiased engineering leader in HVAC and an effective provider of technical datacom information. Since its formation, TC 9.9 has grown to be one of the most active ASHRAE technical committees, and its largest, with roughly 400 members. The committee is represented by a wide range of disciplines within the datacom industry, including, producers of datacom equipment (i.e. computing hardware, software, and services), producers of facility equipment (i.e. HVAC, DCIM, rack, and power solutions), users of datacom equipment (i.e. facility owners, operators, and managers), and general interest (i.e. government, utilities, consultants, academia, and laboratories).

#### **Dustin Demetriou**

Dr. Dustin Demetriou is a Senior Engineer at IBM Corporation in the IBM Systems' Advanced Thermal Energy Efficiency Lab. He received a Ph.D. in Mechanical and Aerospace Engineering from Syracuse University. His research is focused on the analysis, application, and optimization of energy conversion systems, particularly in the area of high-density data centers and high-performance buildings, and the development of advanced electronics cooling technologies. He is the Chair of ASHRAE Technical Committee 9.9 on Mission Critical Facilities, Data Centers, Technology Spaces, and Electronic Equipment.

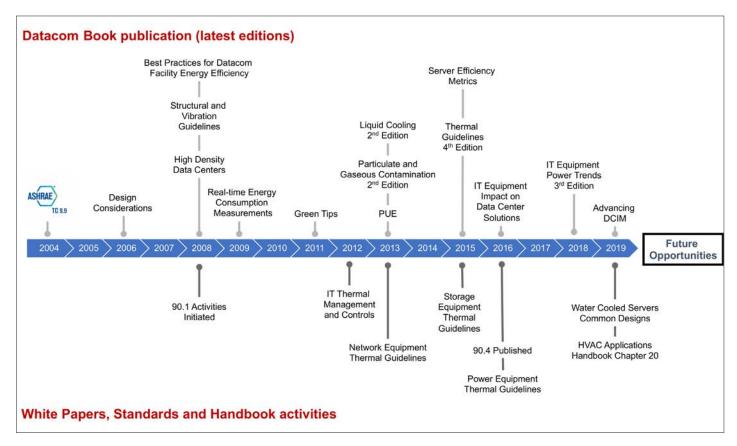

The activities of TC 9.9 have spanned all aspects of data center design and operation. Figure 1 provides a historical perspective on the activities of the committee, dating back to its formation in 2004. One of the cornerstone contributions of TC 9.9 has been the Datacom Series books. The series started with the publication of the Thermal Guidelines for Data Processing Environments and has been expanded to include a diverse range of topics, including data center structural and vibration guidelines, server performance characterization, and particulate and gaseous contamination, to name a few. As of the publication of this article, 14 books have been released with several having multiple editions. These books serve as essential training for anybody with an interest in the datacom industry and have become global resources, with several having been translated into Mandarin and Spanish, and others being incorporated into regulation to support data center energy efficiency initiatives. In addition to the book series, TC 9.9 has played a role in the development of other significant resources. Historically, TC 9.9 has initiated a new topic through the publication of a white paper, which is made freely available to the industry. This allows the material to be published in a timely fashion as either demand is expressed by the industry or a significant gap is seen in the industry by the committee. Subsequently, in many cases, this material is further developed and expanded into a Datacom Series book. To supplement these activities, TC 9.9 also engages in industry/academia research programs. Furthermore, the mate-

rial in these publications is used to develop other resource available through ASHRAE, including a new chapter in the ASHRAE HVAC Applications Handbook [3] and ANSI/ASHRAE Standard 90.4-2016 Energy Standard for Data Centers [4].

The remaining sections of this paper will highlight a few of the most recent activities of the committee that currently have broad interest amongst data center professionals globally.

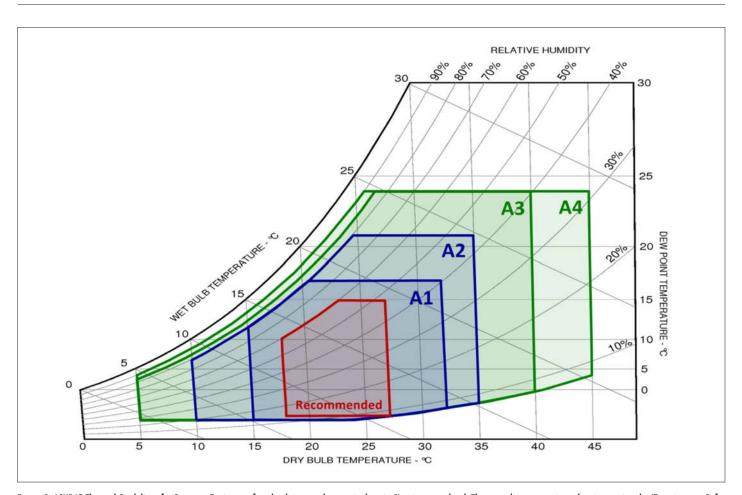

## THERMAL GUIDELINES FOR DATA PROCESSING ENVIRONMENTS

Now in its fourth edition, *Thermal Guidelines for Data Processing Environments* [5], remains the foundation of the Datacom series. When first established, the thermal guidelines represented the first comprehensive set of temperature and humidity conditions, established by the IT manufacturers, that linked the design of datacom equipment (i.e. servers and storage) and the data center. They established guidance to data centers on operating the datacom equipment for optimal performance, highest reliability, and lowest power consumption. This publication has become the de-facto standard for the environmental design and operation of electronic equipment installed in a datacom facility. Furthermore, in 2018, the European Commission approved an Ecodesign Regulation for servers and data storage products [6]. As part of this regulation, IT manufacturers will be required to declare the

Figure 1. Timeline of ASHRAE TC 9.9 activities, including the publication of Datacom Series book, white papers, Standards, and handbook activities since its formation in 2004.

environmental class of their product according to the ASHRAE environmental classes defined in the *Thermal Guidelines for Data Processing Environments* publication.

Prior to publication in 2004 of the first edition, there was no single source in the data center industry for ITE temperature and humidity requirements. In the second edition of the Thermal Guidelines for Data Processing Environments the recommended envelope was expanded to provide data center operators guidance on maintaining high reliability and also operating their data centers in the most energy efficient manner. This envelope was created for general use across all types of businesses and conditions. The second edition also introduced new allowable envelopes (A1 and A2), that expanded the maximum allowable dry-bulb temperature to 32°C and 35°C, respectively, with a maximum relative humidity limit of 80% and a minimum relative humidity limit of 20%. These envelopes also differed in the maximum allowable dew point temperature. These allowable envelopes offered data center operators the flexibility in using an operating envelope that matched their business need and to weigh the balance between the additional energy savings of the cooling system versus the deleterious effects that may be created on total cost of ownership by operating

outside the recommended range. With the further pursuit of energy efficiency, the third edition added two expanded allowable envelopes (A3 and A4) to the already documented A1 and A2 in the second edition. These new classes enabled near full-time use of free cooling techniques in the vast majority of the world's climates. However, using these envelopes added some complexity and trade-offs in terms of energy, reliability, and resiliency that requires more careful evaluation by the data center owner due to the potential impact on the IT equipment to be supported. The third edition also introduced, for the first time, environmental classes for liquid cooled IT equipment (W1—W5).

As the datacom industry looked to further improve data center energy efficiency, from 2011 to 2014, ASHRAE funded research [7] to investigate the risk of electrostatic discharge (ESD) related events in data centers that operate at lower humidity. The results from this study showed that data centers could be operated with relative humidity levels as low as 8% without any noticeable impact on equipment reliability. For data centers that implement a standard set of ESD-mitigation procedures, and as a result of this study, the ASHRAE environmental classes were further expanded to increase the energy saved in data centers by not requiring

Figure 2. ASHRAE Thermal Guidelines for Datacom Equipment fourth edition psychrometric chart in SI units at sea level. These conditions pertain to the air entering the IT equipment. Refer to [5] for additional footnotes, including altitude de-rating and ESD control requirements, before using. (image courtesy of ASHRAE, originally published in [5]).

humidification at low moisture levels. These expanded envelopes are shown in *Figure 2* (see page 29). As has been the case since the second edition, the recommended environmental envelope provides guidance on where facilities should be designed to provide long-term reliability and energy efficiency of the IT equipment. The allowable envelopes (A1—A4) are where IT manufacturers test their equipment in order to verify that it will function but ultimately are meant for short-term operation. The allowable classes may enable facilities in many geographical locations to operate year-round without the use of mechanical refrigeration, which can provide significant savings in capital and operating expenses in the form of energy use.

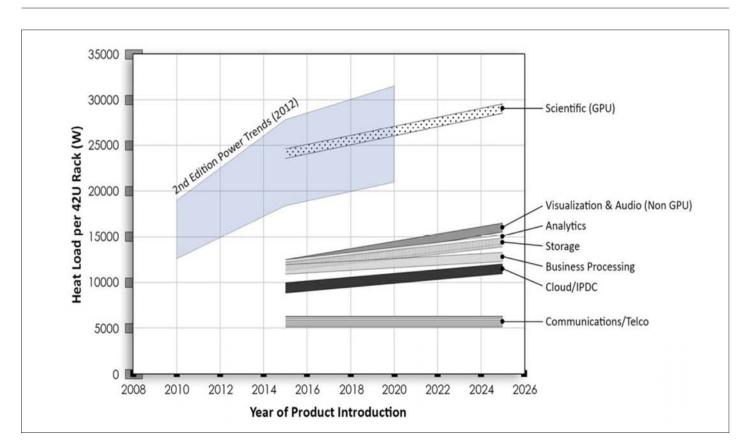

#### IT EQUIPMENT POWER TRENDS

One of the first tasks of the thermal management consortium, referenced above, was the publication of power trends for IT Equipment through the Uptime Institute. About every five years, ASHRAE TC 9.9 has released updated power trends. Now in its third edition, IT Equipment Power Trends [8] (formerly, Datacom Equipment Power Trends and Cooling Applications), contains the best-known hardware power trends through 2025. For the first time in the series, the power trends have been segregated by workload type. This is a significant change from previous editions that focused only on the power trends for servers of a given form-factor (i.e. 1U vs. 2U). By delineating the power trends by workload type, it provides the user with a more customized methodology to assess the power for a

given configuration and/or workload. Of most practical use in the third edition was the inclusion of the compound annual growth rate (CAGR) of power for each workload and server form-factor. Ultimately, data center owners can use the CAGR with measurements of their current system power to get realistic projections of future power needs based on their specific deployment.

The third edition of *IT Equipment Power* Trends breaks down the workload types into eight general categories: Scientific, Analytics, Business Processing, Cloud / Internet Portal Data Center, Visualization & Audio, Communications / Telco, Storage, and Networking. The power trends by workload type reflects the change in the IT industry to support users' needs in terms of server configurations, with targeted types of workloads to maximize IT equipment performance and efficiency. The impact the workload has on the overall power trends is evident from *Figure 3*, which provides a historical perspective of the power trends for 2U, 2-processor servers. It is clear that a similar server, configured differently to meet a specific workload, can have widely different power dissipation. Ultimately, the move to a workload-based power trends should go a long way in helping data center operators design a more efficient data center that supports many generations of IT equipment.

## ADVANCING DCIM WITH IT EQUIPMENT INTEGRATION

The newest book in the ASHRAE Datacom Series, Advancing

Figure 3. Evolution of the ASHRAE Power Trends from the 2nd Edition to the 3rd Edition for 2U, 2-Socket Servers (image courtesy of ASHRAE, originally published in [8]).

DCIM with IT Equipment Integration [9] aims to demystify and extend the implementation of data center infrastructure management (DCIM) tools. With the large number of available data sources within the data center, DCIM has the potential to be the next step in further improving data center energy efficiency and increasing data center resiliency. To enable a more holistic view of the data center, DCIM requires the integration of many disparate data sources—facility equipment, IT equipment, Internet of Things devices, etc. This level of integration has failed to garner wide-spread adoption due to the sheer effort required to program and implement the large number of proprietary protocols, nomenclatures and implementations on the market. ASHRAE DCIM Compliance for IT Equipment (CITE), for the first time, establishes an alignment on a common set of power and cooling telemetry and metrics within the IT industry for servers. ASHRAE TC 9.9 engaged with the industry standards body the Distributed Management Task Force (DMTF) to promote industry adoption of CITE. The DMTF Redfish implementation of CITE provides the proper schema mapping, physical context, and reading properties and has been adopted and accepted into the DMTF Redfish API Schema, release 2018.3.

Advancing DCIM with IT Equipment Integration [9] provides many more details on how an organization can leverage DCIM systems to help normalize and organize the large quantity of data that can be collected and how this data can be used to calculate key metrics to improve the data center's operation. It also highlights key use cases that are already being practiced in many DCIM deployments.

## ANSI/ASHRAE STANDARD 90.4-2016 ENERGY STANDARD FOR DATA CENTER

In 2010, in an effort to promote data center energy efficiency, Standard 90.1 Energy Standard for Buildings Except Low-Rise Residential Buildings [10] incorporated data centers. Prior to this, data centers were exempt due to their mission critical nature. However, data centers have markedly different load profiles and rate of technology innovation compared to the general commercial building industry, making the prescriptive nature of 90.1 relatively unattractive to the data center industry. An ASHRAE Standard 90.4 committee was formed, with participation from ASHRAE TC 9.9. In 2016, ANSI/ASHRAE Standard 90.4-2016 Energy Standard for Data Centers [4], was released. This standard establishes the minimum energy efficiency requirements of data centers for design and construction, guidelines for creating a plan for operation and maintenance, and recommendations for utilizing on-site or off-site renewable energy resources. Standard 90.4 is a performance-based approach that provides flexibility for data center designers to innovate in the design, construction, and operations of their facility.

Standard 90.4 introduced two new design metrics: the mechanical load component (MLC) and the electrical loss component (ELC). Calculations of the MLC and ELC are made and then compared to the maximum allowable values provided in the standard. The MLC can be calculated on either an annualized or design basis and must be evaluated based on the data center's climate zone. The design ELC is the combined losses of three segments of the electrical chain: incoming electrical service segment, UPS segment, and ITE distribution segment. The designer can show compliance with Standard 90.4 by showing that either their calculated MLC and ELC values do not exceed the values contained in the standard at both 100% and 50% of the design IT load or they can follow an alternative compliance path that provides the designer a methodology to allow trade-offs between the MLC and ELC. Standard 90.4 does not use the Power Usage Effectiveness (PUE) defined by The Green Grid. One reason for this is that the PUE is an operational metric based on measured energy use data rather than design calculations. It should be recognized that the design calculations contained in Standard 90.4 would not likely match the actual operational PUE of the data center.

#### **CONCLUSIONS**

ASHRAE Technical Committee 9.9: Mission Critical Facilities, Data Centers, Technology Spaces, and Electronic Equipment remains one the most active technical committees within ASHRAE and the data center industry. The committee is currently focused on a number of efforts, including:

- Research into the impact of high humidity and gaseous contamination on IT equipment reliability.

- Guidelines for energy modeling to show compliance to Standard 90.4.

- Research on developing guidelines for computational fluid dynamics modeling of data centers.

- Creation of expanded content to support the rapidly materializing liquid cooling.

This article was certainly not inclusive of all activities undertaken by the committee. The interested reader is referred to the TC 9.9 website (http://tc0909.ashraetcs.org) for the latest information. The website contains information on TC 9.9 upcoming meetings, previous meeting minutes, whitepapers, and links to purchase the Datacom books.

#### **REFERENCES**

- [1] Schmidt, R, December 18, 2012. "A History of ASHRAE Technical Committee TC9.9 and its Impact on Data Center Design and Operation." Electronics Cooling. Online: https://www.electronics-cooling.com/2012/12/a-history-of-ashrae-technical-committee-tc9-9-and-its-impact-on-data-center-design-and-operation/ [Accessed: July 2, 2019].

- [2] Beaty, D, February 1, 2005. "ASHRAE Committee Formed to Establish Thermal Guidelines for Datacom Facilities." Electronics Cooling. Online: https://www.electronics-cooling.com/2005/02/ashrae-committee-formed-to-establish-thermal-guidelines-for-datacom-facilities/[Accessed: July 2, 2019].

- [3] ASHRAE, 2019. ASHRAE Handbook HVAC Applications. Atlanta: ASHRAE.

- [4] ASHRAE, 2016. ANSI / ASHRAE. Standard 90.4-2016 Energy Standard for Data Centers. Atlanta: ASHRAE.

- [5] ASHRAE, 2015. *Thermal guidelines for Data Processing Environments*, 4<sup>th</sup> edition. Atlanta: ASHRAE.

- [6] Commission Regulation (EU) 2019/424, 15 March 2019. Ecodesign requirements for servers and data storage products pursuant to Directive 2009/125/EC of the European Parliament and of the Council and amending Commission Regulation (EU) No 617/2013.

- [7] ASHRAE, 2015. "RP-1499 The Effect of Humidity on Static Electricity Induced Reliability Issues of ICT Equipment in Data Center." Atlanta: ASHRAE.

- [8] ASHRAE, 2018. *IT Equipment Power Trends*, 3<sup>rd</sup> Edition. Atlanta: ASHRAE.

- [9] ASHRAE, 2019. Advancing DCIM with IT Equipment Integration. Atlanta: ASHRAE.

- [10] ASHRAE, 2016. ANSI / ASHRAE / IES Standard 90.1-2016 Energy Standard for Buildings Except Low-Rise Residential Buildings. Atlanta: ASHRAE.

# JEDEC Thermal Standards: Developing a Common Understanding

**Jesse Galloway**

ON Semiconductor jesse\_galloway@electronics-cooling.com

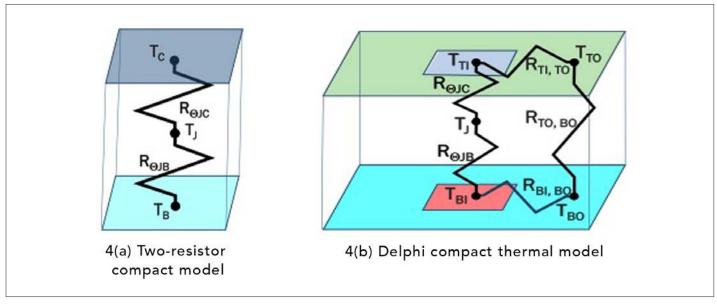

he Joint Electron Device Engineering Council (JEDEC) was established to provide recognized technical standards for a wide range of applications, from how to handle electronic packages and defining package outline drawings, to the methods used to characterize performance, including thermal. The JC-15 committee focuses on writing thermal standards to create a common reference point for generating thermal characterization data. These standards were created with the objectives that they would be meaningful, consistent, and scientifically sound. The primary purpose for adopting and following a standard is to impose a common set of testing conditions so that equivalent results will be measured when the same packages are tested by different labs. This allows end users to compare package performance from different suppliers without concern that improved performance was attributed to more favorable testing conditions. A second application for thermal standards, although often applied incorrectly, is to calculate the junction temperature for a different environment using characterization data measured under JEDEC conditions. Unfortunately, these types of calculations often lead to erroneous estimates if thermal standards are applied incorrectly.

JEDEC thermal standards continue to evolve as more complex packages and test methods are introduced. The body of work developed to date by the JC-15 committee may be organized into three distinct groups. First, standards were written to characterize thermal resistance for single die and multi-die packages. Second, thermal standards were written specifically for LEDs, accounting for the optical component of power transmission. Third, standards were written to document methods for creating simplified thermal network models that represent boundary condition in-

dependent models for electronic packages in a user-defined environment. A historical review of early JC-15 standards is documented in an earlier article [1]. More recent additions to the JC-15 standards are provided in the following sections.

#### 1. Traditional Thermal Resistance Measurements

JC-15 thermal standards provide guidance on the steps required to perform thermal characterization tests and how to report data including chip design, board design, and testing methods. An overview of thermal standards can be found in JESD15-12. Included are definitions for thermal resistance, methods for conducting tests, and suggestions for reporting data.

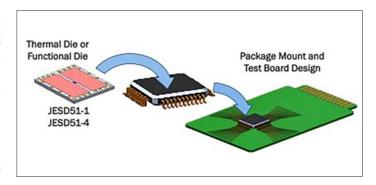

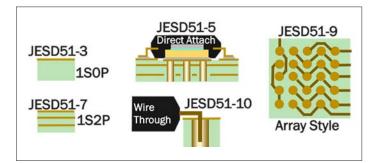

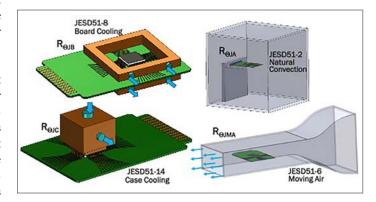

Figure 1. Preparing a package for thermal resistance measurements.

Standards were developed by documenting the steps necessary for preparing experimental test samples. These include test die and test board design as shown in *Figure 1*. JESD51-4 describes the requirements for implementing thermal die (either in wire bond or flip chip format) into a thermal test package.

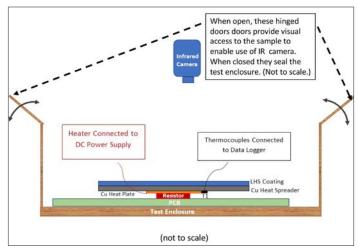

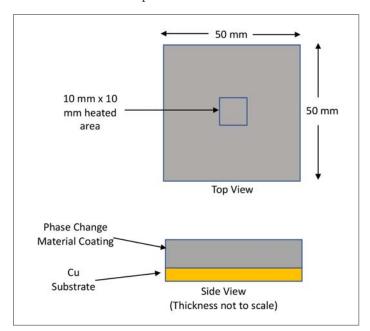

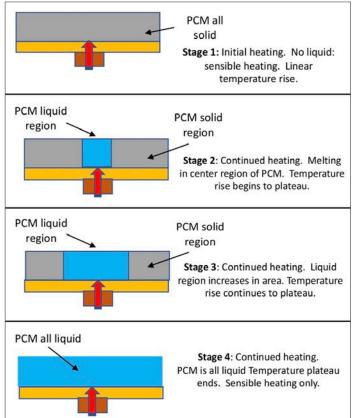

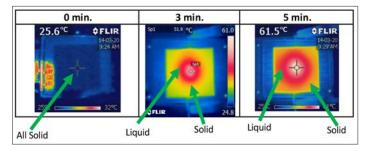

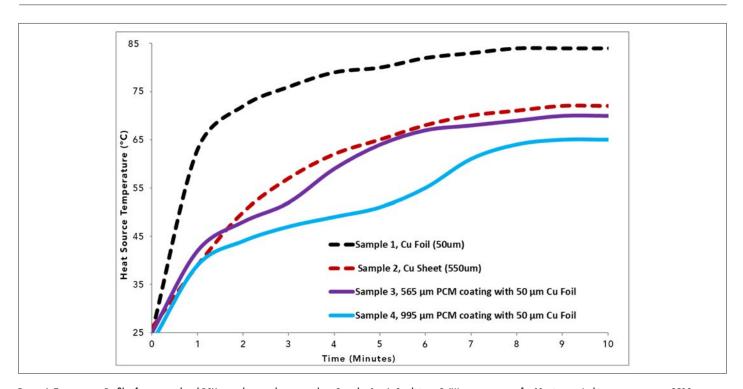

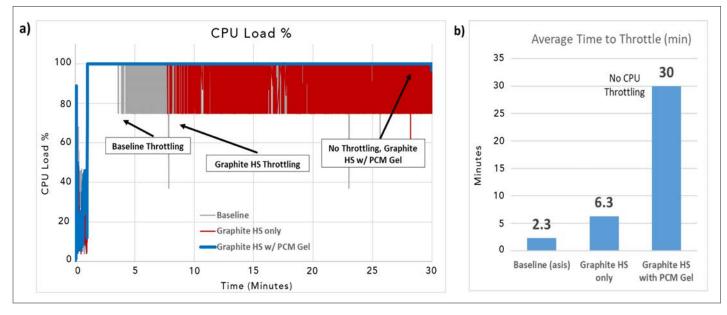

#### Jesse Galloway